### **IMPORTANT NOTICE**

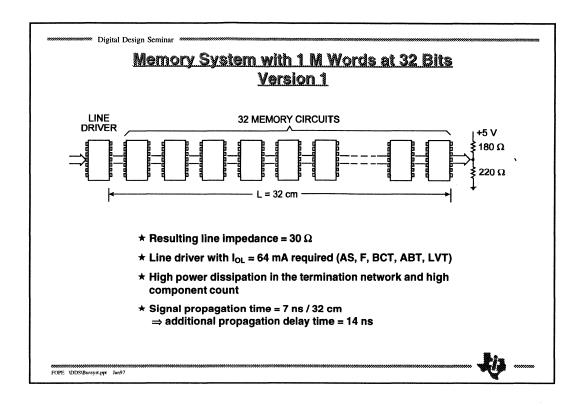

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

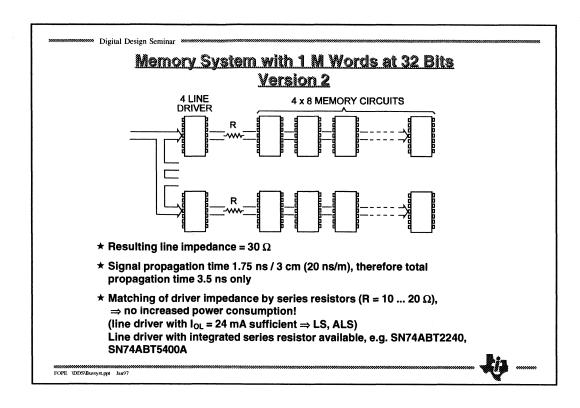

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilised to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SÉMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORISED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products is such application is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimise risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimise inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright ©1997, Texas Instruments Incorporated.

# 1997 Digital Design Seminar

contributions by: Georg Becke

Peter Forstner Eilhard Haseloff

Johannes Huchzermeier

Digital Design Semina

# **Digital Design Seminar**

# Agenda

- **★** Introduction

- **★ Basics and Practical Examples of Transmission**

- **★ Logic Families**

- **★** Metastability

- ★ System Design Criteria

- **★ Bus Systems**

- **★ Advanced Logic Trends**

\DDS\Agenprob.ppt Jan97

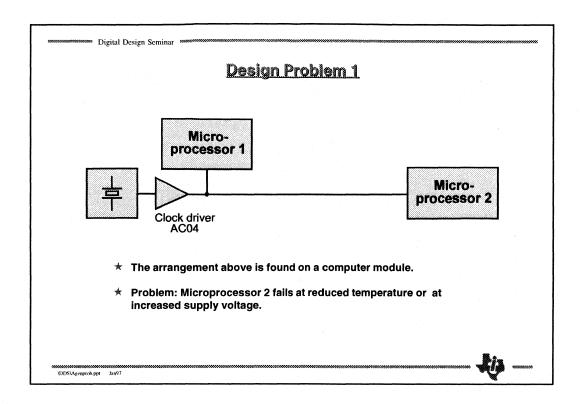

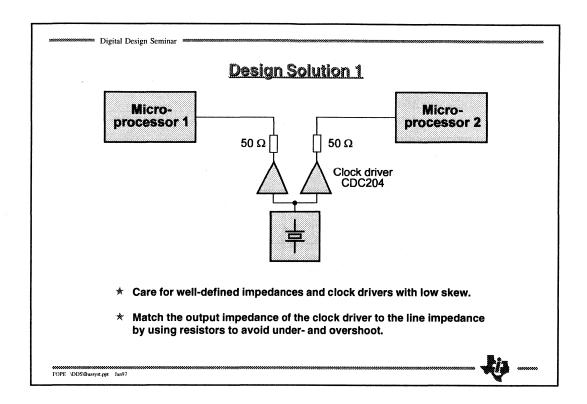

The above example shows a multi-processor system. Both processors get the same clock signal and are running synchronously. The designer builds up the system and finds that at reduced temperature or increased supply voltage Microprocessor 2 fails.

After replacing Microprocessor 2 with a new device, the system still fails. Processor 1 and 2 are exchanged; now Processor 1 fails in socket 2, while Processor 2 works perfectly in socket 1.

Obviously there is a problem with socket 2, but the designer doesn't know what to do.

At the end of the section "Bus Systems", the solution of this problem is found.

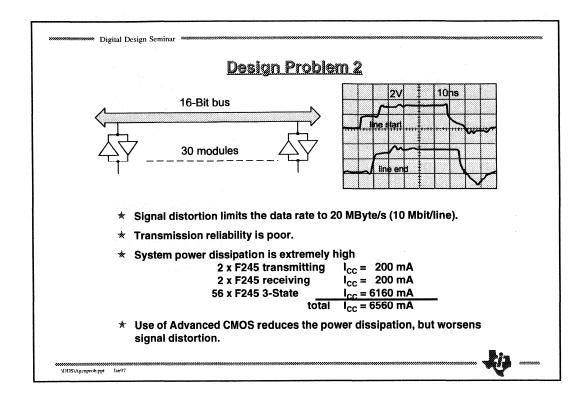

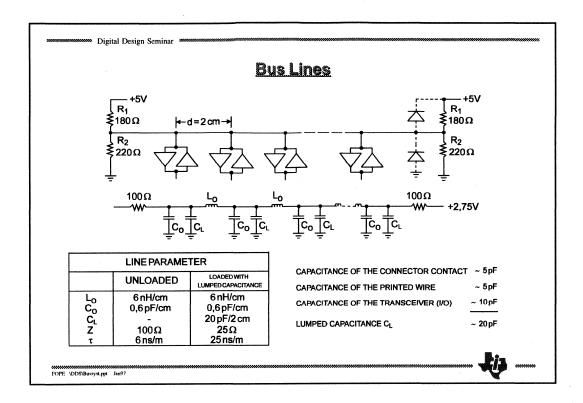

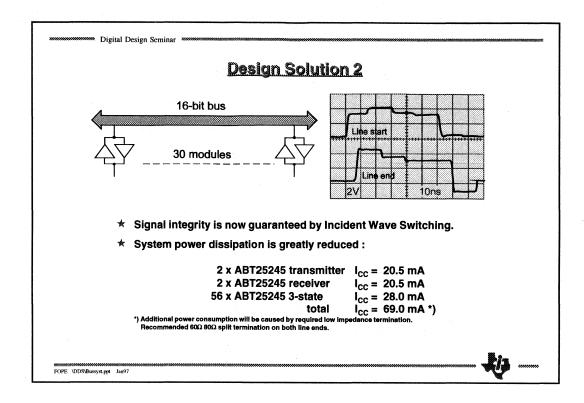

A 16-bit backplane bus with 30 modules plugged into it has to be developed. Because the designer was successful using F245 transceiver in the past, these circuits are chosen to drive the backplane.

A look at the waveforms on this bus with a oscilloscope shows bad signal quality. At the driver output, stairs in the rising edge are observed and at the end of each signal trace there is an undershoot in the range of -1.5V. On the other hand the 60 bus-transceiver has a huge power-consumption. A theoretical calculation shows a worse case supply current of 6.5A for the bus functions only.

The aim is to reduce the power consumption and improve the signal quality. The first idea is to use CMOS circuits, well known for their low power consumption. Replacing the F245 transceiver with AC245 devices reduces power consumption, but the signal quality becomes even worse. The designer had no idea how to improve the bus-system at this point.

To see the solution of this problem, please look at the end of the section "Bus Systems".

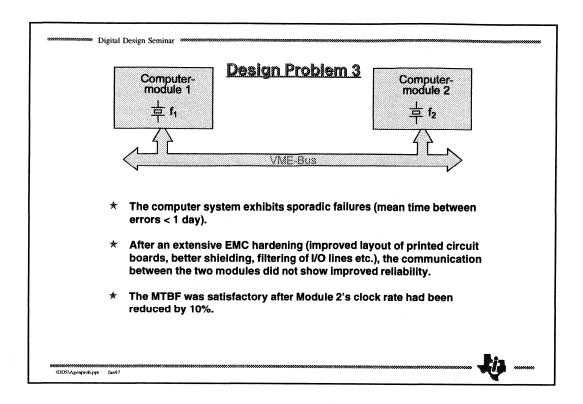

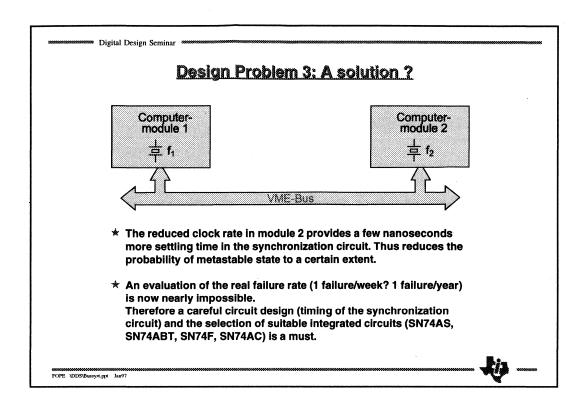

A multiprocessor system, connected through the VME-bus, was designed and running well. After 12 hours, processor module 2 fails; a system reset solves the problem. But again after a further 14 hours, processor module 2 fails again.

Now the designer made a lot of improvements regarding EMC-behaviour, thinking EMC to be the root cause of the problem (introduction of a main-line-filter, new board layout, new metal cabinet, etc. But the improvement was negligible.

Now the designer was desperate and tried this and that. During these experiments he found out that a reduction of  $f_2$  by 10% seemed to solve the problem. But the system requirement was 100%  $f_2$  and not 90%  $f_2$  and so the root cause of failure still needed to be found.

The solution of this problem can be found at the end of the section "Bus Systems".

Digital Design Seminar

# Basics and Practical Examples of Transmission

FOPE \DDS\Transmis.ppt Jan97

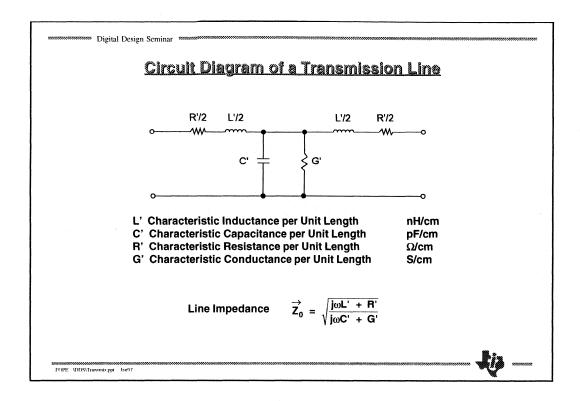

### Circuit diagram of a Transmission Line

The equivalent circuit of a transmission line consists of an inductance L' representing the inductance of the transmission line, a resistor R' representing the ohmic resistance of the line, a capacitance C' representing the capacitance of the line and the conductance G' representing the losses in the capacitance of the line. All these values are length dependent and are therefore specified in unit/length, e.g.: nH/cm, pF/cm,  $\Omega$ /cm, and S/cm. By setting up differential equations, one can calculate the impedance of a transmission line:

$$\hat{Z}_{o} = \sqrt{\frac{j\omega L' + R'}{i\omega C' + G'}}$$

In practice this equation is difficult to handle. First, the line impedance results in a complex number which makes the required calculations time consuming. Second the line impedance is frequency dependent. This becomes uncomfortable in digital circuits, where one has to consider many frequencies simultaneously.

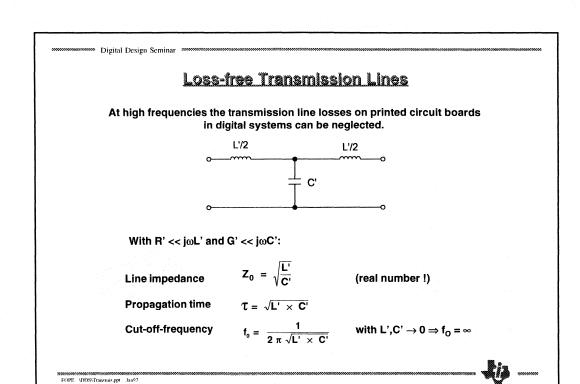

### **Loss-Free Transmission Lines**

In digital circuits low frequencies are not generally of concern. At higher frequencies (above some 10 kHz) the impedance of the inductance  $j\omega L'$  becomes large compared to the resistance R' of the wire. The admittance  $j\omega C'$  is also much greater than the corresponding conductance G'. Under this assumption R' and G' can be neglected. The impedance of the transmission line can now be calculated by the simple formula

$$Z_o = \sqrt{\frac{L'}{C'}}$$

The impedance is now a real number which can be handled like an ohmic resistor. A further advantage is  $Z_0$  is now independent of the frequency.

An important parameter in data transmission circuits is the propagation time  $t_p$  of the signal on a transmission line. This time is also determined by the parameters of the line:

$t_p = \sqrt{L' \cdot C'}$

On typical cables used in transmission circuits (coaxial cable, twisted pair cable) the propagation time becomes  $t_p = 5$  ns/m. This reflects a propagation speed  $v = 200\,000$  km/s (about 60 % of the speed of light).

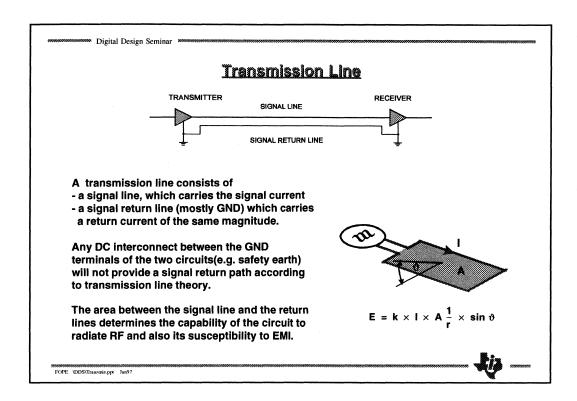

### **Transmission Line**

The designer has to keep in mind that a transmission system always has two conductors: the signal line and the signal return line. Both lines have to be designed carefully to ensure the required quality of the interface circuit. A random signal return path (e.g. via the protective ground wire) is not an adequate signal return line.

Both wires - the signal wire and the signal return wire - act as an antenna which influences the electromagnetic compatibility of the interface circuit. The larger the area between these wires, the larger will be the probability that electromagnetic energy is radiated, which may affect neighbouring equipment. Similarly the area between these wires also determines the electromagnetic susceptibility of the interface circuit.

\* Digital Design Seminar

### Transmission Line Theory

### **Rule of Thumb:**

Transmission line theory has to be applied, when the rise time of the signal is shorter than twice the propagation time.

Example 1 : Twisted pair cable;  $\tau = 5 \text{ ns/m}$ ;  $t_r = 2 \text{ ns}$

$$L = \frac{t_r}{2 x \tau} = \frac{2 \text{ ns}}{2 x 5 \text{ ns/m}} = 0.2 \text{ m}$$

Example 2 : Bus Line; t = 20 ns/m; tr = 2 ns

$$L = \frac{t_r}{2 x \tau} = \frac{2 \text{ ns}}{2 x 20 \text{ ns/m}} = 0.05 \text{ m}$$

With shorter signal lines all line reflections occur during the rise/fall time of the signal. In this case it is allowed to use the simplified capacitive load line model.

FOPE \DDS\Transmis.ppt Jan97

### **Transmission line theory**

Transmission lines have to be treated as lines in accordance with transmission line theory when twice the signal propagation time becomes longer than the rise time of the signal - i.e.: when the line reflections no longer fall into the rise time interval. For a given rise time  $t_r=5$  ns and a typical propagation time of the signal  $t_p=5 \, \text{ns/m}$ , the critical line length in  $l_{\text{max}}=1 \, \text{m}$ . In applications where the propagation time of the signal is much longer - e.g. bus lines - the critical line length is even shorter.

|                                 | L'(nH/cm) | C'(pF/cm)               | <b>Z</b> (Ω) | τ (ns/m) |

|---------------------------------|-----------|-------------------------|--------------|----------|

| Single Wire (far away from GND) | 20        | 0.06                    | 600          | ≈ 4      |

| Space                           | μο        | $\mathbf{\epsilon}_{0}$ | 370          | 3.3      |

| Twisted pair cable              | 5 - 10    | 0.5 - 1                 | 80 - 120     | 5        |

| Flat cable                      | 5 - 10    | 0.5 - 1                 | 80 - 120     | 5        |

| Wire on PC board                | 5 - 10    | 0.5 - 1.5               | 70 - 100     | ≈ 5      |

| Coax cable                      | 2.5       | 1.0                     | 50           | 5        |

| Bus line                        | 5 - 10    | 10 - 30                 | 20 - 40      | 10 - 20  |

### **Typical Line Impedances**

The table shows typical Inductive and Capacitive Layers (L', C') of various signal traces. The last two columns display the corresponding impedance and propagation delay time along the wire calculated from L' and C'.

Common signal traces show an impedance in the range of  $20\Omega$  to  $120\Omega$  and propagation delay times of 4ns/m to 20ns/m.

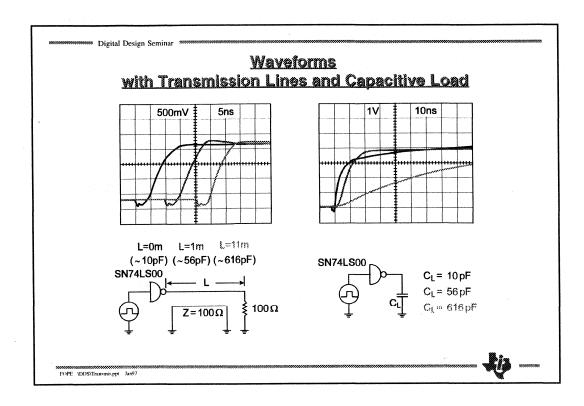

### **Wave-forms with Transmission line and Capacitance Loads**

Transmission line theory says that the line impedance is independent of the line length. As a consequence, the loading of the integrated circuit connected to a transmission line must be independent of the line length. The oscillogram above shows the signal wave-forms measured at the output of an integrated circuit (SN74LS00) when terminated transmission lines of various lengths (I = 0 m, I = 1 m, I = 11 m) are connected to the output of the circuit (the line termination is required to avoid line reflections). The three signals measured are displayed with a time offset for visibility. In all cases the rise time of the signal - and that means also the propagation delay time of the integrated circuit - is not influenced by the line length - say: by the capacitance of the line. The designer however has to consider the propagation time of the signal on the transmission line: a line length I = 11 m results in signal propagation time  $t_p = 55$  ns.

A simple capacitive load caused a high input capacitance of the following circuit - e.g. when driving the gate of a MOS power transistor (Miller effect) - in conjunction with the output impedance of the gate (R  $\approx$  150  $\Omega$  for a SN74LS00) generates a low-pass filter, which increases the propagation delay time of the circuit.

### **Analysis of Line Reflections**

In data transmission systems the designer has to take care of line reflections caused by improperly terminated lines. These line reflections may lead to an additional signal distortion which cause incorrect detection of the value of the signal at the line end (receiver input). This may result in an false operation of the system.

### **Wave-Forms Caused by Line Reflections**

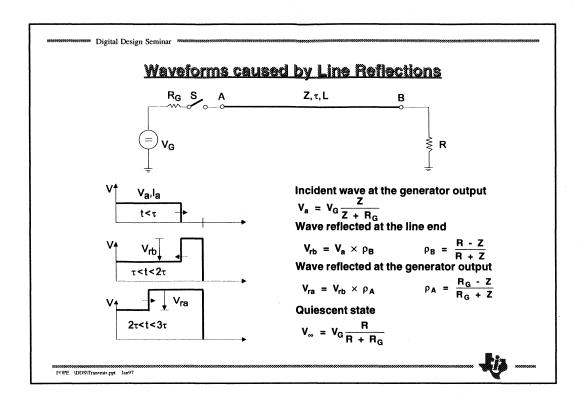

The circuit above shows a simple arrangement to analyse the wave-form in transmission circuits. At the time the switch at the output of the voltage source (generator) is closed, the effective generator load is the impedance of the transmission line alone. The voltage of the incident wave Va<sub>(t=0)</sub> can be calculated by using the simple voltage divider formula:

$$V_{a(t=0)} = V_o \frac{Z_o}{Z_o + R_o}$$

When the wave with this amplitude arrives at the line end, the energy not absorbed in the termination resistor - assuming that the line is not terminated correctly ( $R_t \neq Z_0$ ) - will be reflected back to the generator. The amplitude of the reflected wave at that point is calculated:

$$\label{eq:vr1} \textbf{V}_{r1} = \textbf{V}_{a} \cdot \boldsymbol{\rho}_{B} = \textbf{V}_{a} \frac{\textbf{R}_{t} - \textbf{Z}_{o}}{\textbf{R}_{t} + \textbf{Z}_{o}}$$

When this reflected wave arrives again at the generator output and the output impedance of the generator is not equal to the line impedance ( $R_0 \neq Z_0$ ), again a reflection occurs, where the amplitude of the reflected wave has to be calculated:

$$V_{r2} = V_{r1} \cdot \rho A = V_a \frac{R_o - Z_o}{R_o + Z_o}$$

This process is continued until the energy of the wave is absorbed by the losses of the circuit (termination resistor  $R_t$  at the line end, and output resistor of the generator  $R_0$ ). The final steady-state condition is calculated by the simple voltage divider:

$$V_{t=\infty} = V_o \frac{R_t}{R_o + R_t}$$

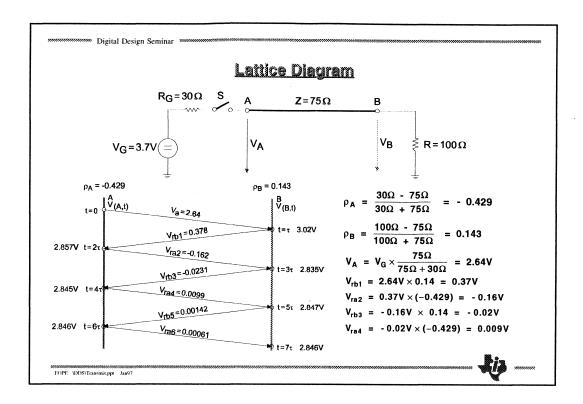

### **Lattice Diagram**

This example shows the analysis of an actual circuit. The generator with an open loop voltage  $V_O=3.7$  V and an output impedance  $R_O=30~\Omega$  represents the simplified equivalent circuit of a SN74F00 in the high state. The line with an impedance  $Z_O=75~\Omega$  may be a coax cable or a printed wire on multi-layer printed circuit board. As one can see, the amplitude of the reflected wave drops very fast. In most application the calculation of the various reflected waves can be stopped after the third reflection since the amplitude of the reflected wave is now so small that it can be neglected (in this example  $V_{rb3}=0.02$  V).

The Lattice Diagram is a useful tool to simplify handling the many numbers to be considered when analysing line reflections. In this simple example the diagram consists of two time scales, each representing the situation at the beginning and at the end of the line. A change of voltage at the generator output is found at every even multiple of the propagation time, at the end of the line at every odd multiple of the propagation time. These points are now connected by lines which represent the forward and backward travelling waves. To each of these lines the corresponding voltage is assigned. The final task left is to add these voltages at the left side of the diagram (beginning of line) of the right side (end of line) to calculate the voltage in the system at a specific time.

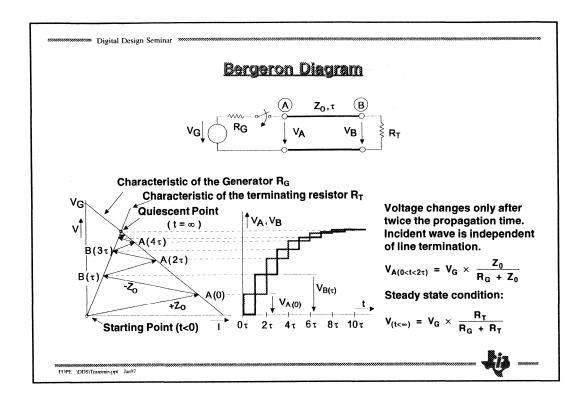

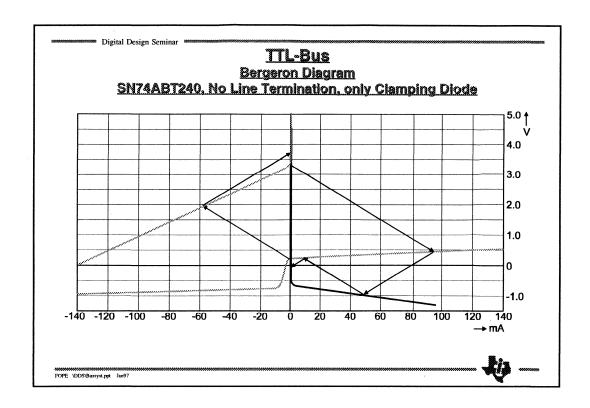

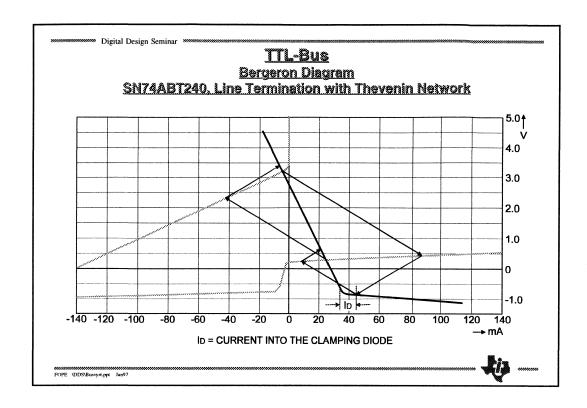

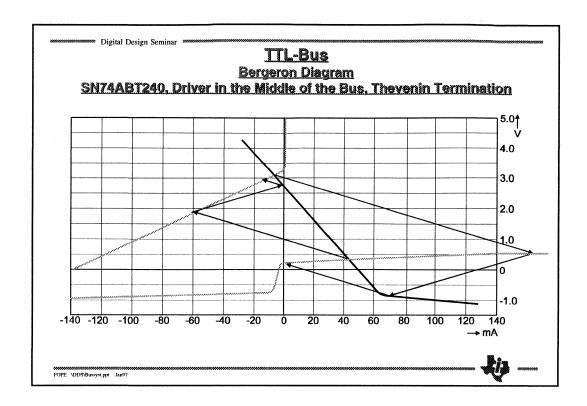

### **Bergeron Diagram**

The Bergeron Diagram is a simple tool to analyse line reflections in circuits which show non-linear characteristics e.g. semiconductor components. For the analysis one has to draw a voltage/current diagram. Into this diagram the output characteristic of the generator R<sub>0</sub> (in this example a linear resistor) as well as the characteristic of the termination at the line end Rt has to be drawn. The point of intersection of these two lines provides the first result: the steady state voltage. The steady-state condition on the line before the switch has been closed ( $V_{t=0} = 0 \text{ V}$ ,  $I_{t=0} = 0 \text{ mA}$ ) is the starting point for the construction of the wave-form. Through this point (in this example the origin of the diagram) a line with the slope of the line impedance  $Z_0$  (tg  $\alpha = Z_0$ ) is drawn. Where this line hits the line which represents the output characteristic of the generator A(0), one gets the voltage of the incident wave. By drawing a line with the negative slope (tg  $a = -Z_0$ ) through the point just constructed, the point of intersection ( $B_{to}$ ) with the line representing the termination characteristic Rt provides the voltage at the line end, when the wave arrives there the first time. By further drawing lines with alternating slopes  $(Z_0, -Z_0)$  one finds the voltages in the circuit during the following build-up. Finally the wave-forms at the beginning and the end of the line can be constructed by using the voltages found during the previous construction.

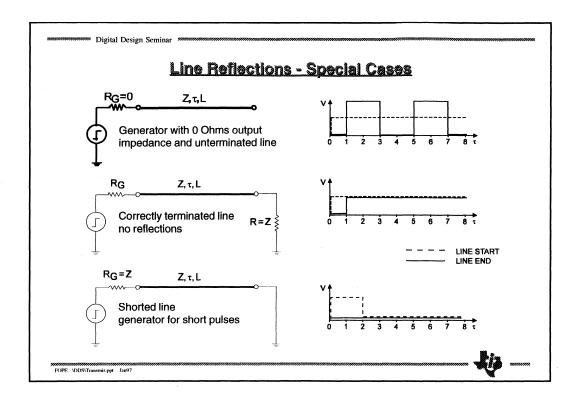

### **Line Reflections - Special Cases**

This picture shows various extreme situations in transmission circuits. In the first circuit a generator with zero Ohm output impedance  $(R_O=0\Omega)$  drives a loss-free transmission line, with an open circuit at the line end  $(R_t=\infty).$  The open circuit may represent the input impedance of integrated circuits, which mostly have an input impedance of several kilo-ohms - large compared with typical line impedance. The reflection factor  $\rho$  = -1 at the generator output and  $\rho$  = 1 at the line end leads to an undamped oscillation at the end of the line. This causes a receiver to switch many times, but not once only as desired.

The next circuit shows an interface terminated correctly at the line end. Under this condition one finds an undistorted signal (no line reflections)

The last circuit shows an interface shorted at the line end. For simpler understanding the output impedance of the generator has been chosen equal to line impedance ( $R_0 = Z_0$ ). When the switch is closed, an incident wave with an amplitude of  $0.5 \times V_0$  travels to the line end and is reflected there with the inverted amplitude ( $\rho$  = -1). When the reflected wave arrives at the generator output again the steady-state is achieved. This circuit is a pulse generator which provides a pulse width equal to twice the propagation time of the wave on the transmission line. Such a circuit can be used advantageously when pulses with a length of a few nanoseconds only have to be generated.

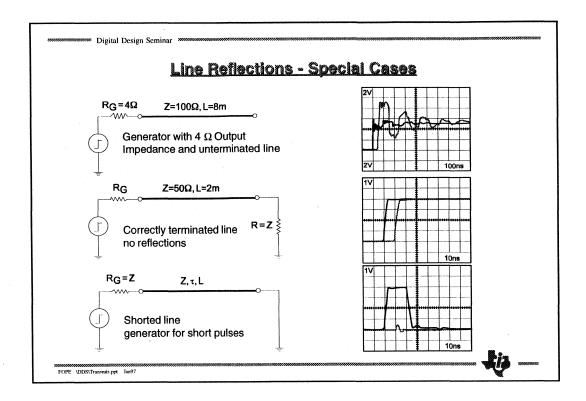

### **Line Reflections - Special Cases**

The circuits described before have been built up to vary the behaviour. It is not as easy to design an generator with an output impedance of  $0\Omega$ . Therefore an Advanced CMOS circuit has been used as the generator. Its output impedance  $R_0 = 8~\Omega$  leads to a damped oscillation, where the first undershoot at the line may still be capable of reaching the threshold voltage of the receiver to cause a false triggering.

The correctly terminated line shows no signal distortion.

In the interface shorted at the end, a coax cable with a propagation time  $t_p = 5$  ns/m and a length l = 2 m has been used. This circuit generates a pulse with a width  $t_d = 2 \times 5$  ns/m  $\times 2$  m = 20 ns.

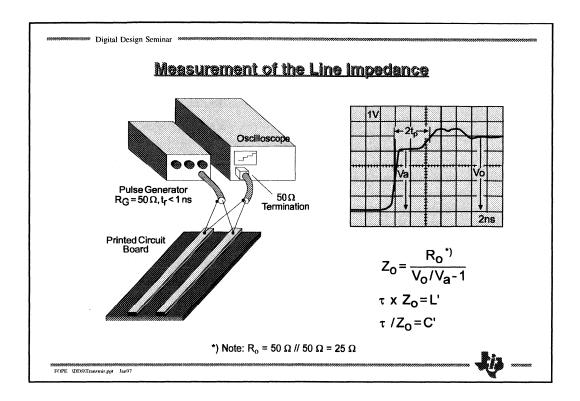

### **Measurement of the Line Impedance**

For correct design of an interface (selection of the generator, termination of the transmission line), knowledge of the impedance of the transmission line in use is necessary. One way to determine the line impedance is by means of a L/C bridge where one measures the inductance of a transmission line shorted at the end (short circuit impedance  $\approx$  inductive layer L') and capacitance with the line open at the end (open circuit impedance  $\approx$  capacitive layer C'). This method however mostly requires expensive equipment which often is not available.

A simpler method is shown on the picture above, where one needs a fast pulse generator and an oscilloscope only. By applying this method one measures the amplitude of the incident wave  $V_a$  caused by the voltage divider 'output impedance of the generator / line impedance' (in this example a signal and a ground wire in parallel on a printed circuit board) as well as the steady-state voltage  $V_O$ . By using the following equation (the voltage divider formula solved to  $Z_O$ ) one gets the line impedance  $Z_O$ :

$$Z_o = \frac{R_o}{\frac{V_o}{V_a} - 1}$$

where  $R_{O}$  is output impedance of the generator. In this measurement set up the output impedance is made by the two coax cables in parallel, therefore  $R_{O} = 25 \Omega$ .

By measuring the propagation time  $t_{\text{p}}$  one can also determine the inductance and the capacitance per unit length:

$$L' = t_p \cdot Z_o \qquad C' = \frac{t_p}{Z_o}$$

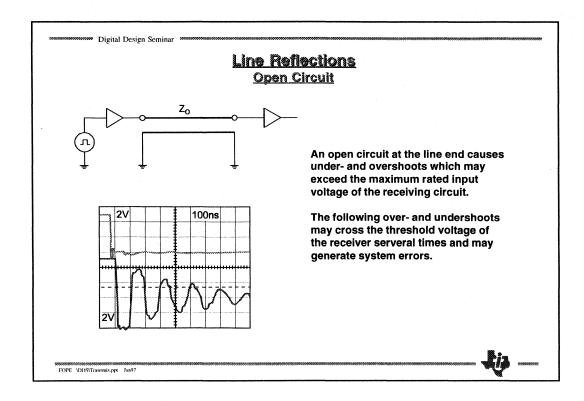

### **Line Reflections - Open Circuit**

Driving an unterminated transmission line with a low-impedance output generates a good signal quality at the beginning of the line, while at the end of the line oscillation can be observed. This corresponds to the first example of our "Special Cases".

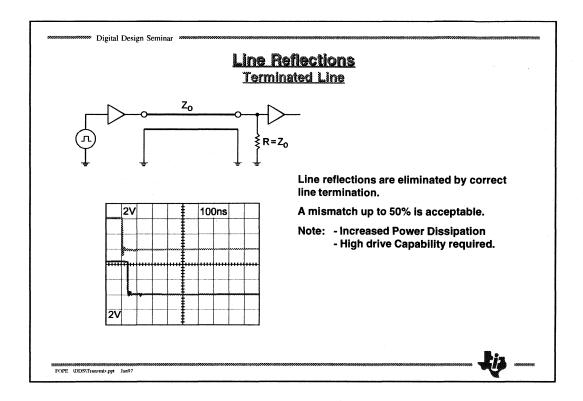

### **Line Reflections - Parallel-Terminated Line**

Transmission lines are parallel-terminated at the line end by a resistor between the signal line and the signal return line. If the termination resistor is chosen equal to the line impedance ( $R_t = Z_0$ ) no line reflections are found. In many applications, a mismatch of up to 50 % is acceptable. Under this condition the resulting reflection factor will be  $\rho = 0.2$ .

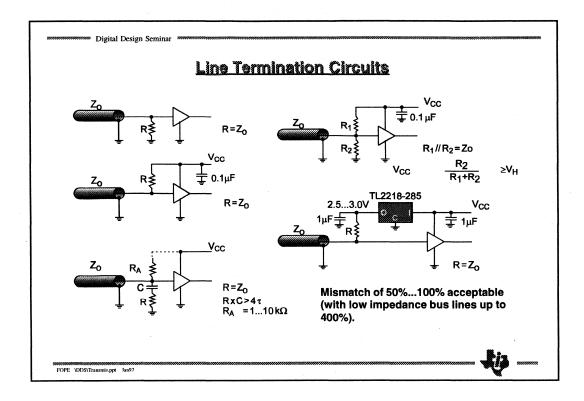

### **Parallel Line Termination Circuits**

Single-ended or unbalanced transmission lines are usually terminated by a resistor between the line end and signal grounf. If the drive capability of the generator in high state is not sufficient - e.g. open collector or open drain outputs - the termination resistor can also be placed between the line and the positive supply rail. This rail for low frequencies is shorted to ground via the power supply and for high frequencies via the decoupling capacitor (typical  $0.1~\mu F$ ).

Particularly in CMOS applications, the designer does not like the continuous current in the termination resistor. This current increases the power dissipation. The current can be blocked by placing a capacitor  $C_b$  in series to the termination resistor  $R_t$ . When the time constant  $R_t \times C_b$  is about 4 times the propagation time of the interface circuit, the line is almost sufficiently terminated.

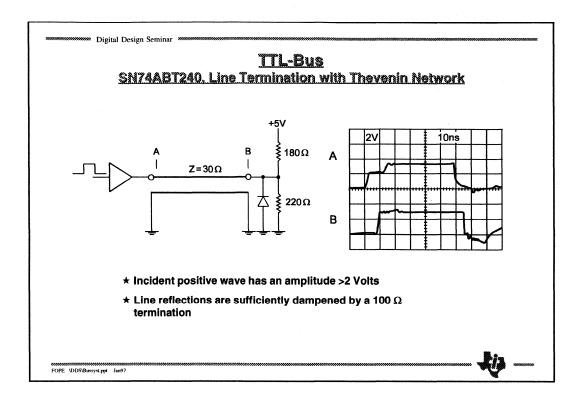

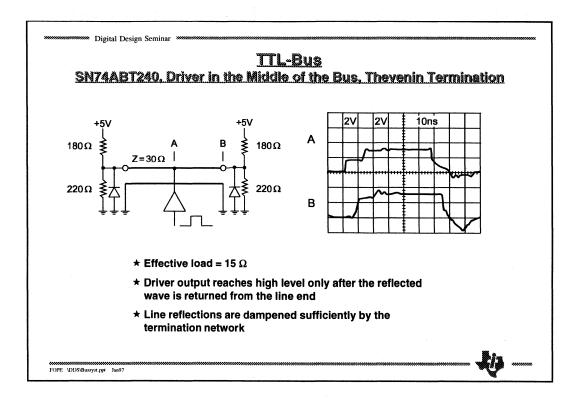

In TTL systems, a resistor divider is often found at the line end (split resistor or Thevenin termination). This circuit is adapted ideally to the drive capability of TTL circuit and performs well in terms of eliminating line reflections. However the disadvantage of this arrangement is the large DC current through the resistor divider.

In advanced interfaces therefore often a circuit is used, which is called Active Termination. Here the termination resistor is placed between the line end and the output of an additional power supply, which provides an output voltage of 2.5 ... 3 V. Since on average 50 % of its active time the line is in the high state, the supply current is reduced by this amount. This termination technique is also used in bus applications, where much of the operating time all bus drivers are in inactive mode (3-state). In this situation the supply current becomes zero. Last but not least, the pull-up resistor avoids the line floating when all bus drivers are in the 3-state.

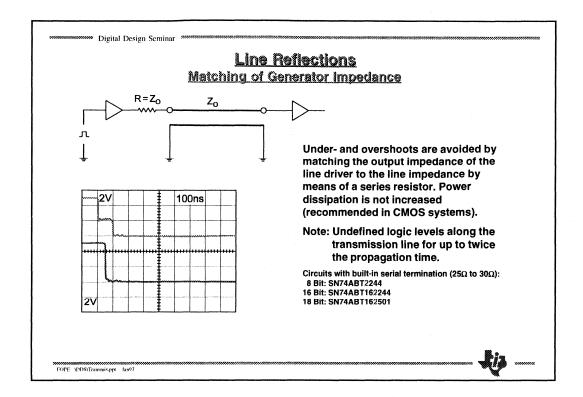

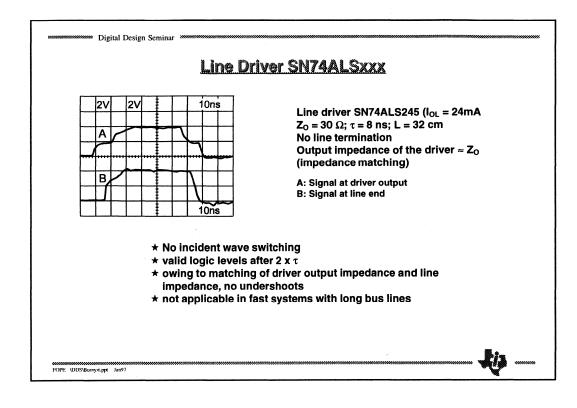

### **Line Reflections - Matching of Generator Impedance**

An elegant method to avoid under and overshoots at the line end is to match the output impedance of the driver circuit to the line impedance by placing a resistor in series with the output. A different output impedance of the driver in the low and the high state mostly does not allow correct matching. As long as the output impedance of the circuit in question is chosen to be 60 % to 100 % of the line impedance, a reasonable signal quality can be expected at the line end (receiver input). This technique is applicable in uni- and bi-directional point-to- point interfaces. In multipoint applications, where several stations are located along the transmission line, this technique is not recommended due to the long settling time of the signal (up to twice the propagation time).

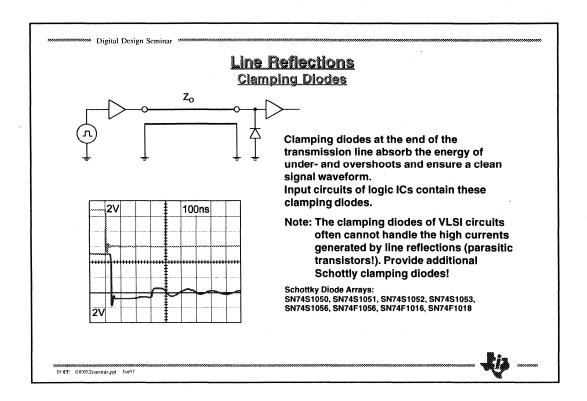

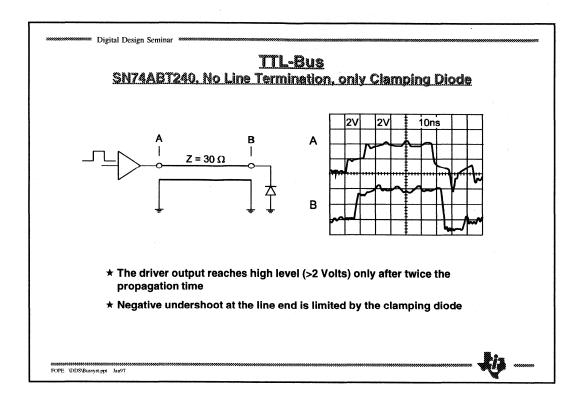

### **Line Reflections - Clamping Diodes**

An effective method to avoid excessive under- and overshoot at the line end is to limit this by means of clamping diodes. As the picture shows, a negative transition at the begin of the transmission line causes a negative undershoot at the line end which amplitude is limited to the forward voltage of the clamping diode at the line end ( $\approx$  0.7V). The energy stored in the transmission line is not absorbed totally. Therefore one can observe several waves travelling forward and backward on the line. However their amplitude is a few 100 mV only.

Due to the positive influence of these diodes, clamping diodes are integrated into all logic circuits. TTL circuits contain at their inputs clamping diodes to the ground terminal to limit negative undershoots. In a CMOS environment, where owing to the higher voltage swing the positive overshoots are also of concern, additional clamping diodes between the input and the positive supply rail are often incorporated.

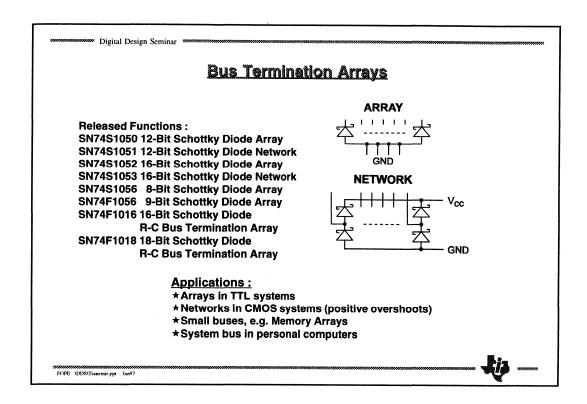

### **Line Reflections - Bus Termination Arrays**

To reduce the number of required components, Texas Instruments offers the Bus Termination Arrays:

These circuits include clamping diodes for 8- to 16-Bit circuits. Depending on the device type, the designer can select between clamping diodes to GND only or two rows of clamping diodes, one to VCC and one to GND.

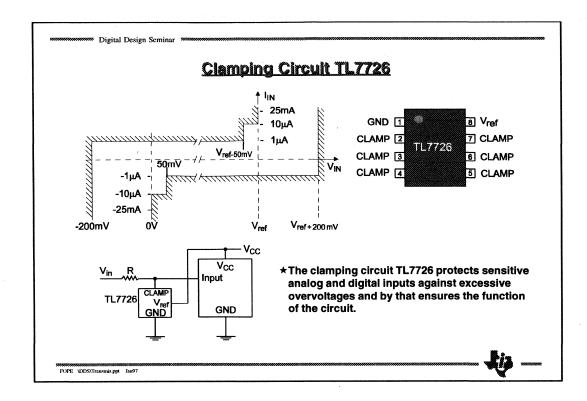

### **Line Reflections - Clamping Circuit TL 7726**

The clamping circuit TL7726 protects sensitive analog and digital inputs against excessive overvoltages and thus ensures the function of the circuit. It limits the overand under-shoots to a maximum of +/-200mV by sourcing up to 25mA of clamping current.

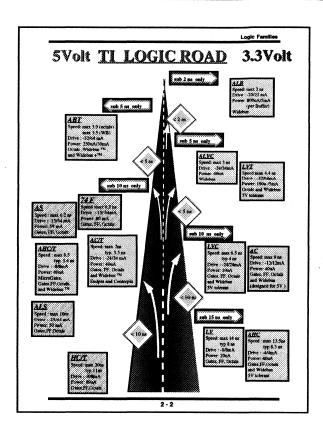

You always drive well with TI - on the ASL road.

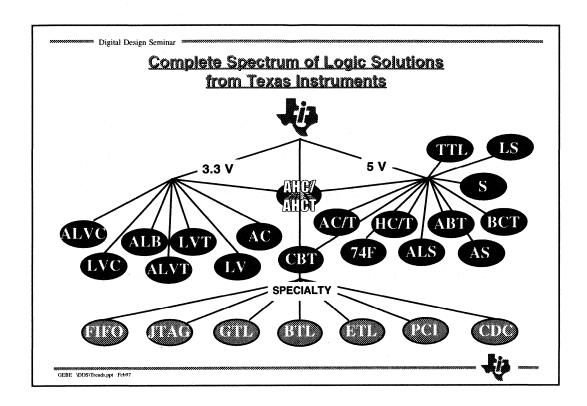

This road shows different Logicfamilies, selected by speed.

The right side comprises TI's 3.3V Logoc families, while the left side shows the 5V Logic families.

One can see that there are only a few bipolar families mentioned on this foil:

AS,74F and the ALS family. This are families which are still in a sold in a huge volume.

This shows where TI wants to go: TI goes CMOS.

The performance data for each family is shown in the box.

Also one can see that there are some families specified at different voltages:

The AC family and the AHC family have an additional specification at 3.3V, but were designed originally for 5V.

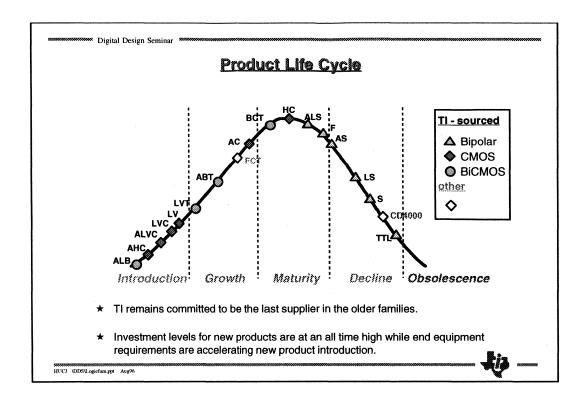

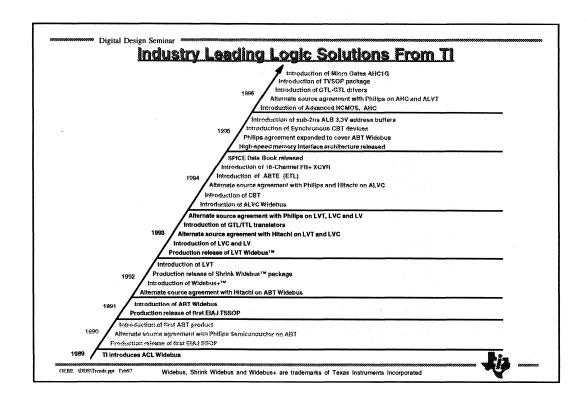

The Product Life Cycle curve shows all available logic families from TI.

This cycle is divided into 5 sections, beginning on the left side with the introduction phase and ending on the right side with obsolescence.

One can find that all bipolar families are in the decline phase. Those are not recommended to be used in new designs.

Today's system trends, such as increased packaging density, higher operating frequencies and reduced heat generation (e.g. no need for a cooling fan), lead to a strong need to reduce the power consumption or to change to low power technologies. This limits the use of mature technologies like LS and F. Even for HCMOS there is an improved version available: AHC Advanced HCMOS.

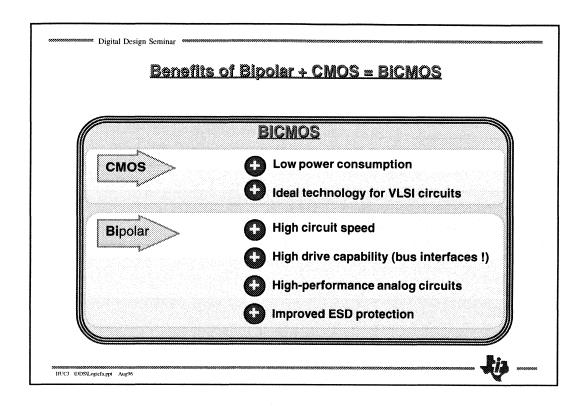

With the development of BiCMOS, a combination of Bipolar and CMOS technologies, the high drive capability and low noise characteristic of bipolar technology and the low power consumption of CMOS technology have been combined.

TI has true second source agreements with Philips Semiconductor and Hitachi Semiconductor for the Advanced BiCMOS Technology (ABT) family as well as for the low-voltage families (LV, LVC, LVT, ALVC). The agreement with Philips has recently been extended to also cover ALVT and AHC.

Investments for new products are at an all time high while end equipment requirements are accelerating new product introduction.

On the other side, TI remains committed to be the last supplier in the older families.

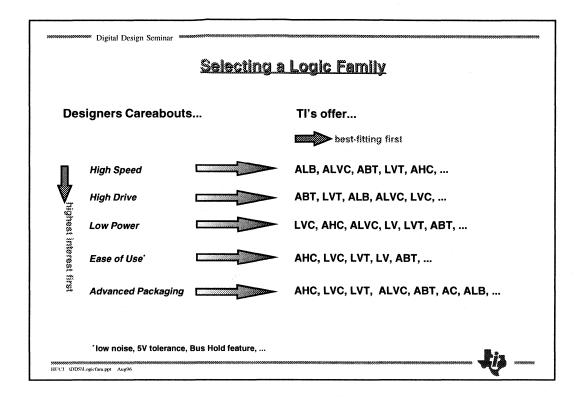

Customer careabouts for selecting the optimum logic family are diverse depending on application needs and targetted end-equipments. From a survey, recently conducted by TI, the ranking of customer careabouts are as shown above.

According to this survey the careabouts have been sorted by importance from top to bottom.

The logic families have been sorted from left to right with regard to the most suitable family for a given criteria.

For example: you are looking for the fastest logic family?

Choose the row 'High Speed' and look for the first family in 'TI's offer': ALB

It doesn't matter which focus you have; TI offers always the optimum logic family for your application.

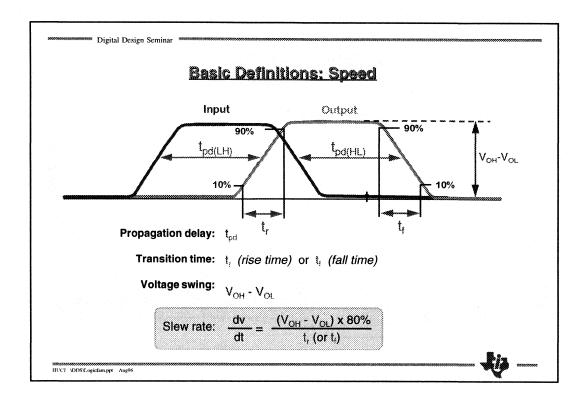

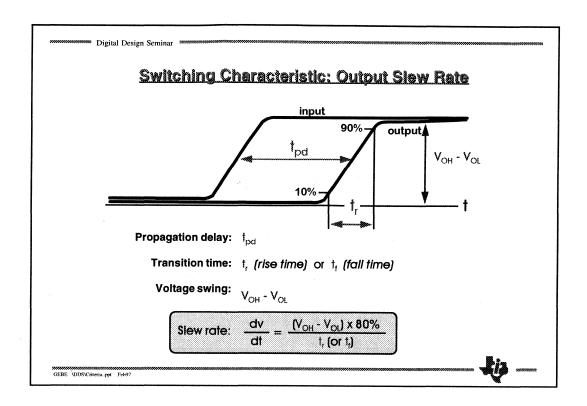

There are two parameters a designer may have in mind when mentioning "speed". The more frequently used refers to the circuit's propagation delay,  $t_{\rm nd}$ .

The shorter the  $t_{pd}$ , the higher the speed.

Some engineers, however, also refer to "circuit speed" in the context of a device's signal slew rate. As can be seen from the formula, a circuit's slew rate corresponds to the transition (rise or fall) time of the output signal.

The shorter the rise or fall time, the higher the slew rate.

As will be shown on the next page, propagation delay and slew rate are not necessarily proportional.

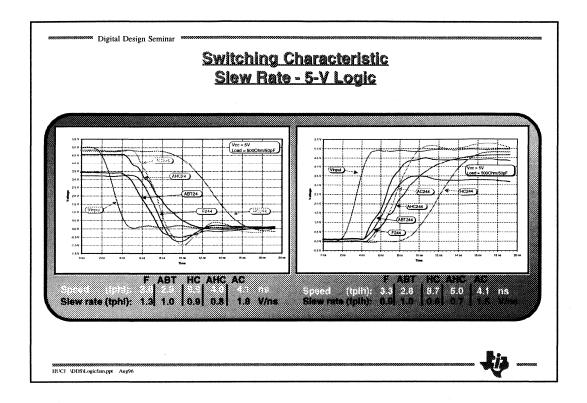

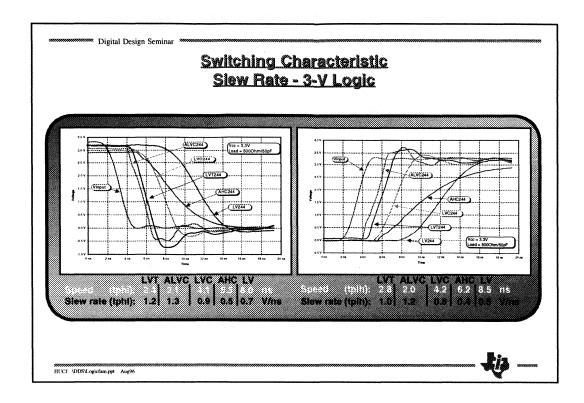

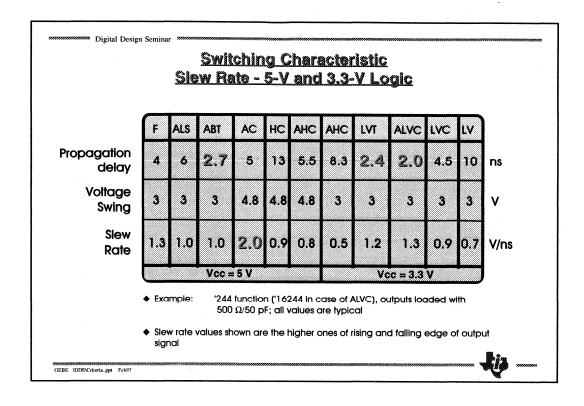

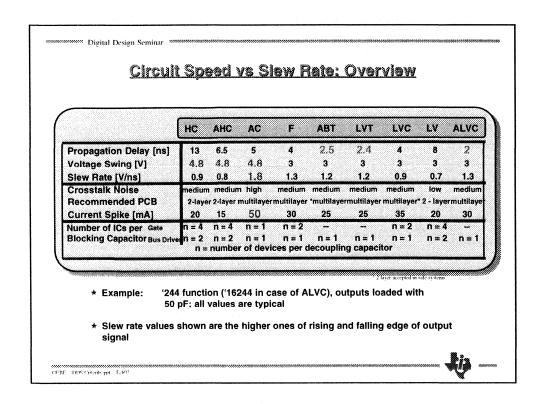

This and the next page show propagation delays ( $t_{pd}$ ), voltage swing ( $V_{OH}$  -  $V_{OL}$ ) and slew rates (dv/dt) for selected 5V and 3V logic families.

F, ABT, HC, AHC and AC are operating from a 5V supply voltage, while LVT, ALVC, LVC, AHC and LV have a 3.3V supply (next page).

The data may indicate that  $t_{pd}$  and dv/dt show common trends, but a closer look points out that there is no direct link between the two parameters. For example, the fastest family (ABT) is <u>not</u> the one with the highest slew rate. Another example is AHC, which is characterised by a three-fold speed improvement over HCMOS, but shows lower slew rates.

As will be discussed later in this section, high slew rates are often unfavourable, as this leads to high noise levels generated by the components. The worst technology in this respect is 5V AC, while AHC gives very positive results.

Slew rates must be considered especially when designing high speed systems.

These graphs show propagation delays ( $t_{pd}$ ), voltage swing ( $V_{OH}$  -  $V_{OL}$ ) and slew rates (dv/dt) for selected 3V logic families (LVT, ALVC, LVC and LV) and AHC operated at Vcc=3.3V (as specified in the datasheet).

In comparison to 5V logic, all of the low voltage technologies have somewhat lower signal slew rates.

It should be especially noted that ALVC, the fastest of all technologies shown, exhibits an uncritically low slew rate.

Circuit design techniques and the use of SSOP or TSSOP packages makes this favourable characteristic available.

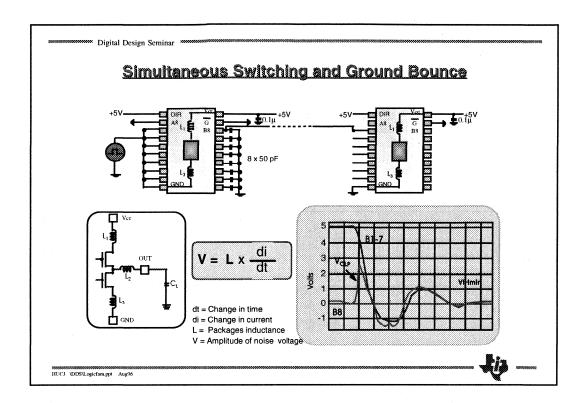

A widely accepted method of measuring ground bounce is to switch (N-1) device outputs, while keeping the Nth input at a Low level.

The outputs of the drivers which are switching react with a certain delay to the changes at the inputs, whilst the unswitched output should remain undisturbed at "L" level. But, crosstalk from the neighbouring pins, a brief dip in the supply voltage and a brief rise of the groundlevel (resulting from the inductance of the Vcc and ground connections) automatically cause a reaction at the corresponding output.

The best results are achieved by the 48 pin Widebus package. This is primarily because of the 8 distributed GND pins for the 16 integrated drivers. The traditional 8 bit 'corner pin' devices are provided with only one GND pin and therefore show poor behaviour.

It is also necessary to mention that the measured values of noise level depend on the process technology used.

Whereas with BiCMOS and bipolar devices the threshold level will normally not be exceeded, with fast CMOS logic 2V or more may be reached as a result of the steeper pulse slope of CMOS signals, and consequently higher effect on the lead inductance.

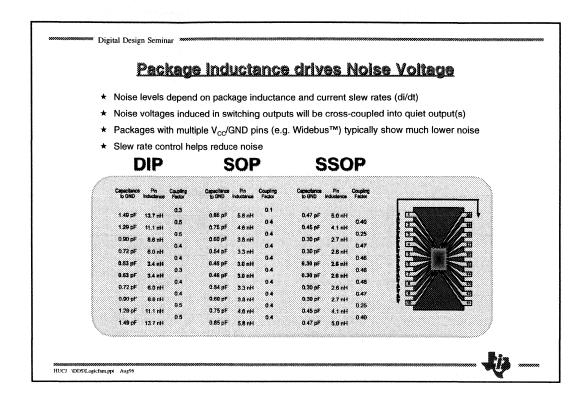

There are three factors which determine the electrical characteristics of a package:

- 1) the capacitance of a pin to ground

- 2) the inductance of a pin

- 3) the coupling factors of the pins to each other

In particular, the supply voltage pin should have a low inductance, and all signal lines of a good package should have as low as possible of all these three parameters.

The table above shows capacitance, inductance and coupling factor of each two neighbouring pins. These parameters are determined by:

- the length of the connections to the pin within the package,

- the spacing between these connections,

- the length of the wirebonds.

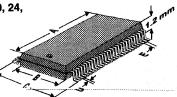

A DIP package has significantly longer internal connections than SOP or SSOP (and TSSOP). A long connection results in a high inductance and a high coupling factor; the increased area caused by the long connections also results in a high capacitance.

However, the reduction in coupling factor achieved by the short connections is partly offset by the smaller spacing between them.

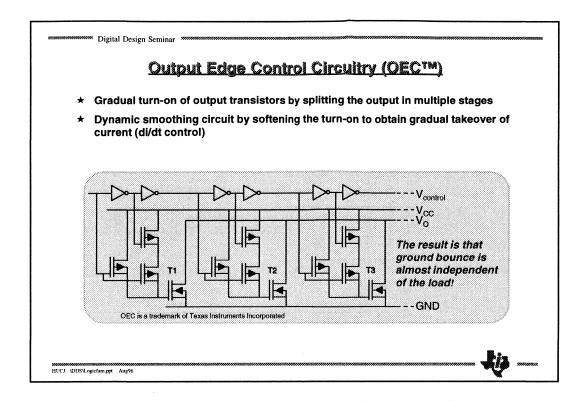

Signal slew rate improvements seen in Advanced Logic circuits have mainly been achieved by designing the circuits' output stages such that the change in output current (di/dt) and correspondingly the change in output voltage (dv/dt), are under control.

For this purpose, Texas Instruments has developed a technique called

## Output Edge Control (OEC™)

The use of parallel output transistors that are turned on one after the other limits the signal slew rate.

A side effect is that the output noise levels are almost independent of the circuit load.

OEC has been implemented in AC, LVC and LVT.

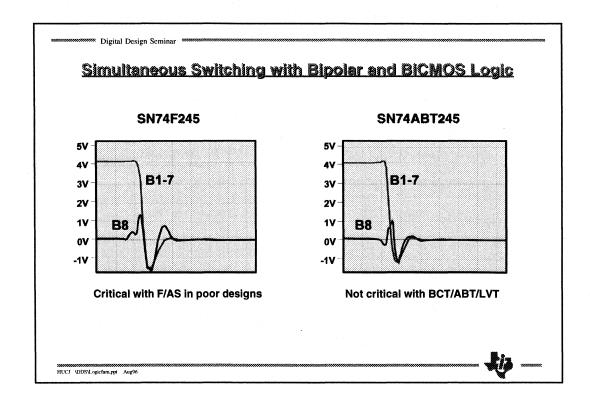

Comparing ABT with 74F logic on simultaneous switching noise, one can recognize that the device of the F-family shows a more critical behaviour than the ABT device.

The maximum undershoot of the F device is greater than -1.5 V, while the ABT devices show a maximum value of about -800mV only.

Ground bounce behaviour must be taken into account very carefully for the design of digital systems using fast bipolar and CMOS technology families such as F/AS or AC/FCT.

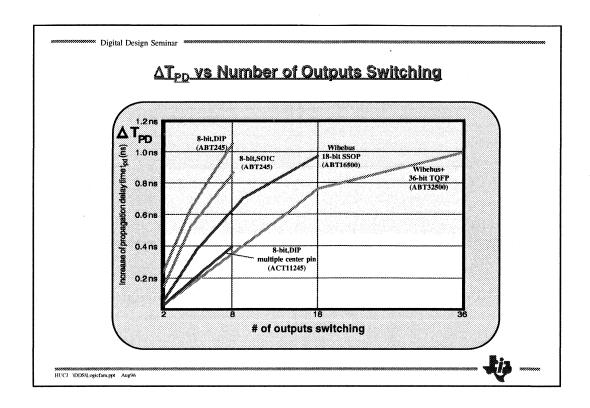

The propagation delay of the component also depends on the number of simultaneously switched outputs.

The reason is that the inductance of the supply leads acts as a "current brake".

For devices in conventional packages (DIP and SOP) an additional delay of 150 to 200 ps for each output switched needs to be taken into account.

For example, an SN74F244 will have a maximum delay  $tp_{HL} = 7.5$  to 8 ns, if all eight outputs switch simultaneously.

In this respect, the multiple  $V_{CC}$  leads in Widebus<sup>TM</sup> circuits are of advantage. They may not eliminate the effect, but at least they insure that the loss of speed is no greater than in octal bus drivers, even though twice as many outputs are switched.

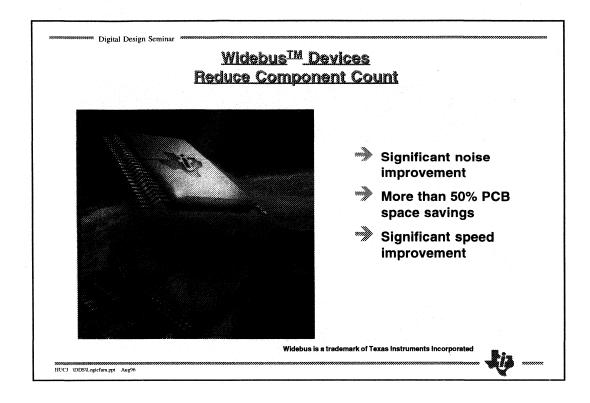

Widebus<sup>™</sup> circuits offer designer substantial advantages, when it comes to designing advanced systems.

With the growing performance demands that are being made of computer systems, one has to expand the width of bus systems to 16 or 32 bits, so that high data throughput can be achieved. As the available space for a circuit is limited, this can only be implemented with components like Widebus<sup>TM</sup>, which support wide bus architectures at an attractive cost.

As circuits become faster, the electrical characteristic of the package becomes more and more the focal point. Besides the unavoidable capacitances of the leads, it is primarily their inductances that determine the response of fast digital circuits and which, in some cases, limit their usage.

In addition, doubling the transfer channels in the new circuits reduces the component count by 50%.

Each of these new components is no bigger than a conventional 24-pin SO package, as the new circuit uses only 50% of the area previously used.

| ABI<br>Advanced<br>BICMOS<br>Technology    | 16 Bits                                                     |                                                             |                                                             | 18 Bits                 |                                                           |                                      | 20+bits                                                     |                                                           |                                      |                                                          |

|--------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------------|-----------------------------------------------------------|--------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------|----------------------------------------------------------|

|                                            | 16240<br>16241<br>16244A<br>162244<br>16245A<br>162245      | H16245<br>16373A<br>16374A<br>16470<br>16540                |                                                             | 16833<br>16853<br>16952 | 16500B<br>162500<br>16801<br>162501<br>16600              | 162601<br>16823                      |                                                             | 16260<br>162260<br>16460<br>162460<br>16821<br>16827      | H18504A<br>162827<br>16841<br>162841 |                                                          |

| AC/I<br>Advanced<br>CMOS                   | 16240<br>18241<br>16244<br>16245<br>16254<br>16255<br>16373 | 16374<br>16470<br>16540<br>16541<br>16543<br>16544<br>16620 | 16623<br>16640<br>16646<br>16648<br>16651<br>16652<br>16657 | 16833<br>16952          |                                                           |                                      | 16472<br>16474<br>16476<br>16423<br>16825<br>16863<br>16864 | 16821<br>16827<br>16841<br>16861                          |                                      |                                                          |

| AHC/I<br>Advanced<br>High-Speed<br>CMOS    | 16244                                                       | 16245                                                       | 16373                                                       | 16374                   |                                                           |                                      | 10004                                                       |                                                           |                                      |                                                          |

| LVC<br>Low<br>Voltage<br>CMOS              | 16241A                                                      | 16245A                                                      | 16374A<br>16540<br>16541A                                   | 16646                   |                                                           |                                      |                                                             |                                                           |                                      |                                                          |

| ALVC<br>Advanced<br>Low<br>Voltage<br>CMOS | 16244A<br>H16244<br>H162245                                 | H16543                                                      | H16827                                                      |                         | H16524<br>H16525<br>H162525<br>H16821<br>H16825<br>H16823 | H16863<br>H16901<br>H16500<br>H16501 | H16601<br>H162601                                           | 16260<br>H162260<br>H162268<br>16269<br>HR162261<br>18270 |                                      | H162820<br>16821<br>16827<br>162827<br>H162721<br>H16841 |

| LVT<br>Low<br>Voltage<br>Technology        | 162244                                                      | 16373<br>16374<br>16543<br>16646                            | 16952                                                       |                         |                                                           | 16500<br>16501<br>16825<br>18602     | 182502                                                      | 18504<br>182504                                           |                                      |                                                          |

TI offers more than 160 Widebus<sup>TM</sup> functions.

The excellent electrical behaviour of Widebus<sup>™</sup> packaging is used for devices operating from 5V and 3V supply voltage.

For 5V families TI offers ABT and AC as well as some functions in the new AHC family.

For 3.3V supply voltage Widebus<sup>TM</sup> is available for LVC, ALVC and LVT.

Widebus+ $^{\text{TM}}$  supports up to 36 bits within one single package.

## Nomenclature:

8

SN74 FAM HR 162 xxx ADL,

18

<u>32</u>

FAM = Logic family

H (optional) - BusHold- feature,

8 - Octal device with JTAG functionality

16 - Widebus<sup>TM</sup>

18 - Widebus™ with JTAG functionality

32 - Widebus+TM

2 - Series damping resistor B-Port

R,2 - Series damping resistor A- and B- port

xxx - function

A - Die Revision

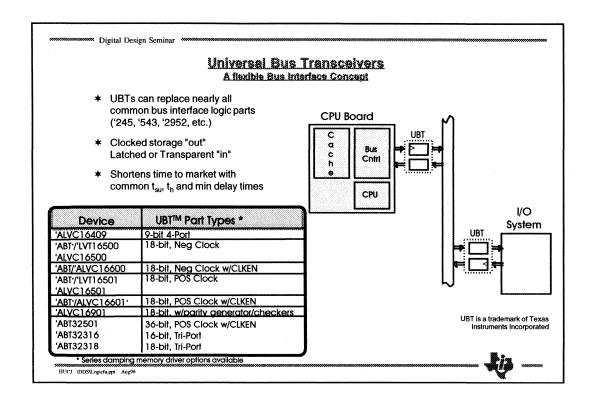

DL - Package (here SSOP)

Many high performance applications require more than one mode for accessing their system bus, because different parts of the system have different data access and processing speeds. While some may be able to work in transparent mode (fully synchronous to the data source), others will require data to be latched, to meet setup and hold time requirements. When designing CPU access to the bus, clocked storage is the easiest method.

UBT<sup>TM</sup>'s are bi-directional transceivers that can be configured as

- \*transparent,

- \*data-flow-through transceivers (e.g. '245 function),

- ★latch-enabled transceivers (e.g '543 function),

- ★clocked registered transceivers (e.g. '646 function),

- ★ and clock-enabled registered transceivers (e.g. '952 function).

Designed specifically for workstation bus-interface applications, the UBT<sup>TM</sup> is perfect as an interface to many different microprocessor architectures and system backplane specifications available. It may also be cost effective in low volumes as an alternative to several different interface functions.

Advanced BiCMOS technology (ABT) is available from Texas Instruments, to help designers develop high performance bus systems.

It was designed to provide speeds equivalent to existing advanced bipolar solutions with 90% less power consumption.

ABT employs a submicron 0.8µm process technology.

It combines elements of both bipolar and CMOS circuits on a single silicon chip.

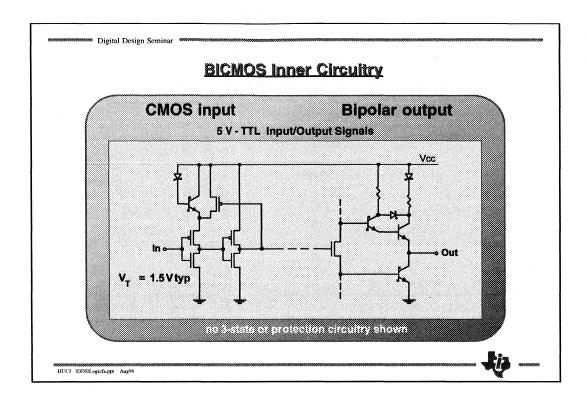

ABT is based on a CMOS core-circuit structure with an NPN bipolar output transistor module.

From a power (current) consumption standpoint, the use of bipolar in the output stage is advantageous for two reasons:

- the voltage swing is less than that of a CMOS output. The power consumed when charging or discharging internal circuit capacitances and the external load capacitance is reduced.

- 2) the bipolar transistors are capable of turning off more efficiently than CMOS transistors. The wasteful flow of current from  $V_{cc}$  to GND is reduced.

Although bipolar tends to have a high static power consumption, its lower dynamic power consumption allows for better overall power performance at high frequencies than either pure bipolar or CMOS as the dynamic power makes up the majority of a device's overall power consumption.

Simplified input and output stages of an ABT transceiver are shown on this slide.

The inputs are designed to offer TTL- compatible levels with guaranteed switching between a  $V_{IH}$  minimum of 2V and a  $V_{IL}$  maximum of 0.8V.

As these inputs are implemented in CMOS circuitry they offer high impedance for low leakage and low capacitance for minimal bus loading.

(The CMOS supply voltage of the input stage is dropped by diode D1 and transistor Q1, centering the threshold around 1.5V).

ABT outputs utilizes bipolar circuitry to provide the speed and drive necessary for a bus interface. A major advantage of bipolar circuitry in the output stage is the reduced voltage swing, which lowers ground noise, improves signal integrity and reduces dynamic power consumption.

Because of its small process geometry, tight metal pitch and shallow junctions, ABT can provide for strong output drive currents (sink current 64mA, source current 32mA) and low capacitances. As a result of these enhancements, internal propagation delay are very fast and show good behaviour regarding noise.

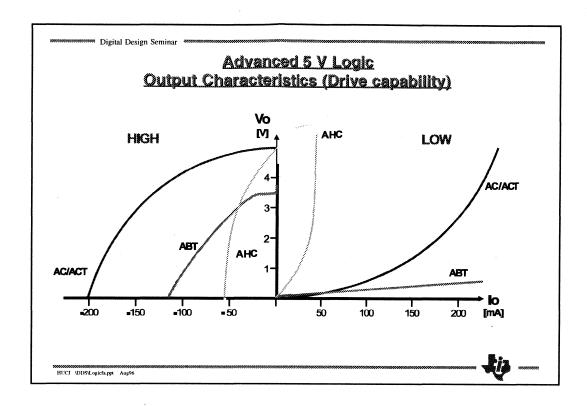

The curves show the drive capability in the logic 'high' and 'low' - states for various logic families.

The steeper the H- (L-) curve, the higher the drive capability.

To be noticed: ABT is a BICMOS family and delivers TTL levels at their outputs (typical output high: 3.6 V).

These curves can be taken as base for the graphical calculation of over- and undershoots of a certain family.

For the Bergeron method, as mentioned earlier, two more parameters are necessary: the **line impedance** and the value of the **line termination resistor**.

An example is given on the next page.

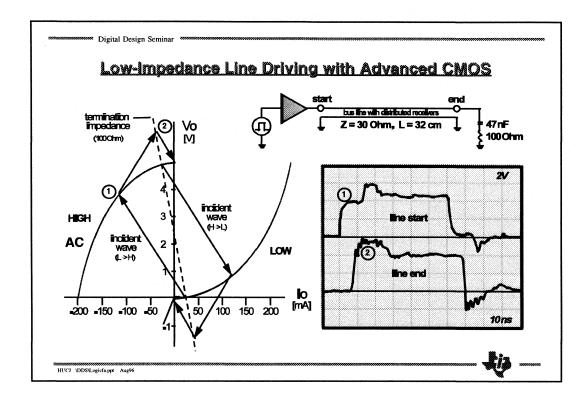

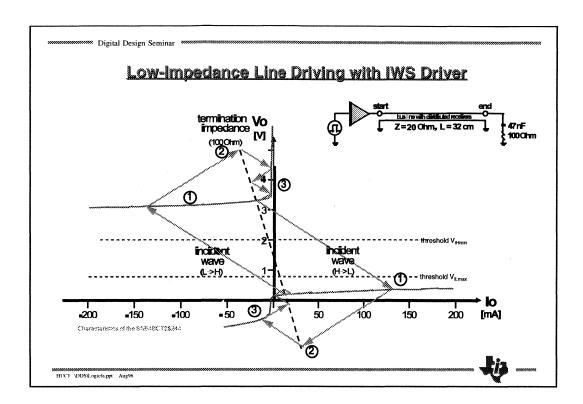

As an example of the graphical Bergeron method, a low impedance line is evaluated.

The set up is as follows: A line driver AC is connected to a line which impedance is  $Z_0 = 30$  Ohm, the length of the line is 32 cm. The line is terminated with 47nF in series with 100 Ohm. The generator delivers a digital signal, duty cycle 50%.

The first step to solve this problem graphically is to choose the output characteristics of the AC driver.

The termination resistor of the setup together with the duty cycle (50%) results in the dashed straight line. The line impedance  $(Z_0)$  results in the steepness of the progressing waves (solid arrows).

Each crossing of Output characteristic and the solid arrow can be recognized as voltage value at the begin of the line (Output driver).

Each crossing of termination curve and the solid arrow can be recognized as voltage value at the end of the line (termination resistor)

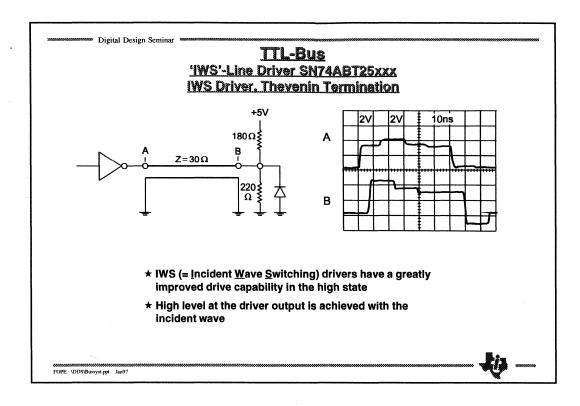

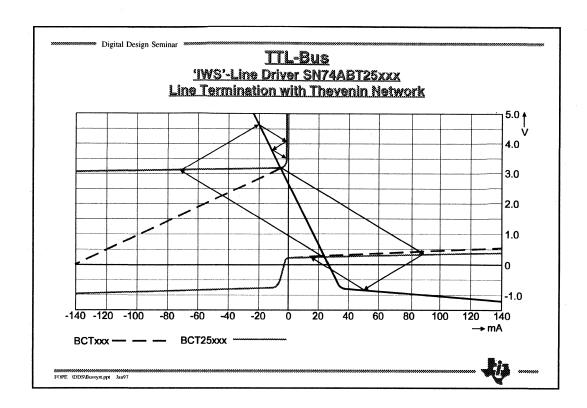

For the same set-up as before, but with the line impedance changed down to 20 Ohms, the Bergeron method is applied, using an BCT25244, an Incident Wave Switching (IWS) driver instead of the AC driver.

The graph shows that again with the 1.wave a change of the logic level is ensured, which would not be achieved by using the AC driver earlier.

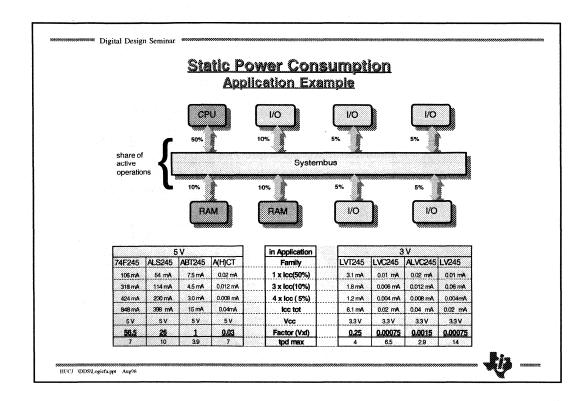

This foil shows an application example in a computer system.

CPU, RAM and I/O ports are connected via a bus. The percentage value shows the share of activity on the bus (e.g. the CPU uses the bus for 50% of the time). If we assume that all components used for this application are taken from the same family and we set up four identical systems, we can compare the performance.

The 74F family uses the highest power consumption for the application. This family is made in bipolar technology and consumes in tristate the same current as during active operation. Also the propagation delay time is the slowest with 7 ns.

ABT has improved performance in both power consumption and speed. ABT devices are made in BiCMOS Technology. During tristate-mode the power consumption is decreased down to 190 microamps. The speed is increased by 44% against the 74 F family.

A comparison with ALVC shows that only 0.15% of the ABT power consumption is used by ALVC. Also the propagation delay is improved to a value of  $T_{pd}$ =2.9 ns.

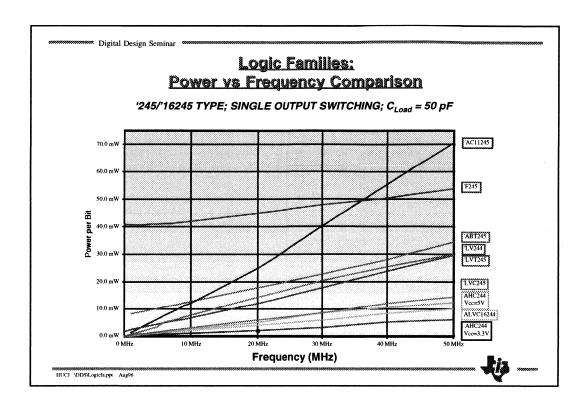

This foil shows the dynamic power consumption of different 5V and 3.3V Logic families.

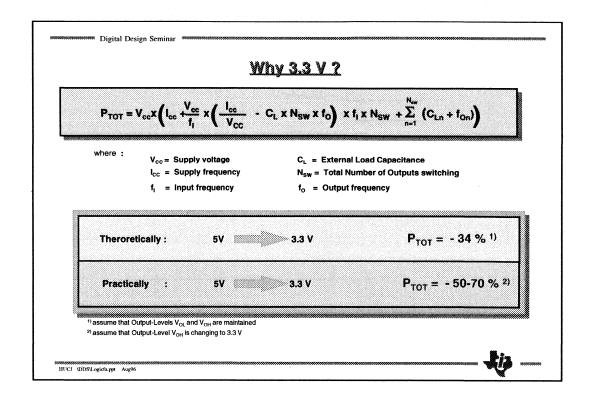

The answer to the question: "Why 3.3V" is given by the formula for determination of the power consumption related to logic circuits, here as example the formula for CMOS devices ( CMOS level inputs) .

A logic circuit's total power consumption,  $P_{TOT}$ , is strongly influenced by a number of parameters. If we investigate this formula, we can split this into two parts:

- 1) V<sub>CC</sub>

- 2) the 'rest', which is determined by various parameters such as number of outputs, frequency, etc.

Some are inherent to the technology, like the static  $I_{CC}$  currents and the so-called "current spike" ( $I_{SP}$ ), that flows across the output during circuit switching. Others depend on load conditions, operating frequency, and so on.

However, the parameter with the most significant effect on the overall power consumption, is  $V_{\text{CC}}$ .

The theoretical saving of power dissipation is 34%, if you reduce the voltage from 5V down to 3.3V.

Practically, the power saving will be about 50-70%, because other parameters are also improved by reducing the supply voltage.

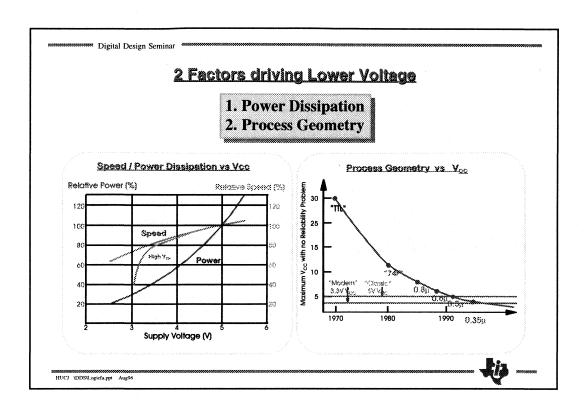

Changing a system's  $V_{CC}$  from 5V to 3.3V by reducing a circuit's supply voltage will worsen its speed. However, as the figure on the left shows, the relative loss of speed is much less than the improvement in power consumption.

Practically, most system designs do not allow for any speed degradation. The way out for suppliers is to use process technologies with smaller feature sizes that (often even over-) compensate the speed loss. This results in the availability of 3.3V logic families that offer the same or higher speeds than the 5V families they replace, in combination with a drastic reduction of the power consumed.

The significant improvement in power consumption is only one reason why there is such a strong momentum in the industry to migrate towards reduced supply voltages.

Another strong push to reduce  $V_{CC}$  is driven by the accelerated use of small process geometries. Advanced microprocessors or ASICs sometimes employ several millions of transistors. This demands process feature sizes of 0.5 micron and below. Unfortunately, such small process geometries start to show reliability problems, if operated with a 5V supply voltage. Some types of equipment, e.g. industrial control systems, are therefore frequently forced to change their  $V_{CC}$  to 3.3V, although their operating environment would still allow for the high power consumption of 5V designs.

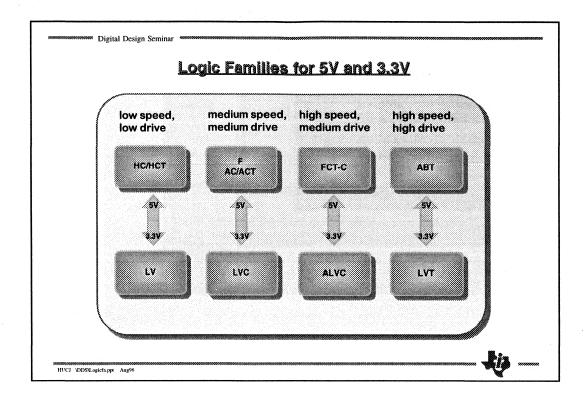

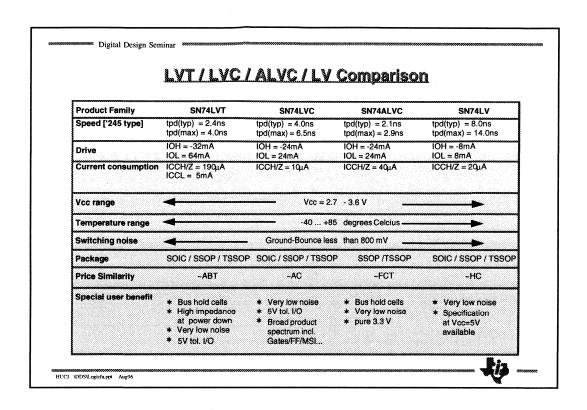

Texas Instruments' Low Voltage Logic families have been designed to provide a performance that is at least equivalent to, but usually even better than, that of commonly used 5V devices.

If you are in the situation to design a new application with 3.3V logic, but are only familiar with the performances of the 5V logic families, this foil will help you.

LV is somewhat comparable to the well-known LS and HC/HCT families, but features improved speed.

**LVC** addresses the medium performance range, where families like F or AC are predominant in 5V applications.

Two different solutions are available for high performance 3.3V system design:

**ALVC** combines medium output drive with very high speed performance (unmatched by any other 3.3V logic family).

**LVT**, which is the 3.3V equivalent to the 5V ABT family of bus interface devices, combines speed with a drive capability that is high enough for reliable operation of large backplanes.

These four families of 3.3 V logic devices can be used for portable applications from electronic games up to high performance engineering workstations.

The LVT family is the only low voltage family using BiCMOS technology.

LV, ALVC and LVC families are manufactured in CMOS technology.

The LVC and the LV families are designed for low cost 3V Systems such as consumer equipment, portable computers, electronic games, toys, portable telecom equipment that require medium performance at low cost.

The ALVC family, with a typical propagation delay time of 2 ns has been designed to meet the requirements of high speed systems including engineering workstations and interfaces to SDRAM-modules.

The LVT family, with its high drive capability, can be used for Backplane/Bus Driving applications, high-performance engineering workstations, desktop-PC's and telecom transmission/switching equipments.

TI has second source agreements with Philips and Hitachi for all of these four Low Voltage Logic families. The agreement with Philips has recently been extended to cover other new logic families like ALVT and AHC.

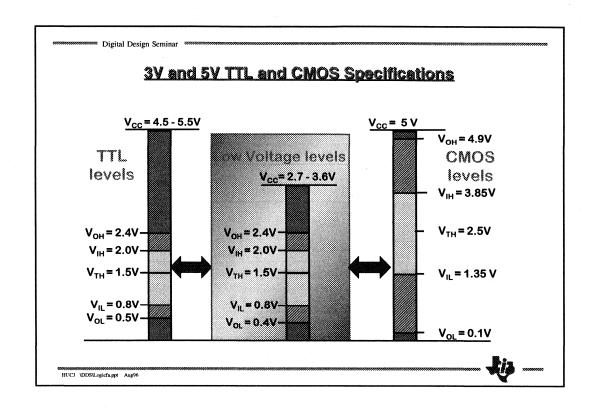

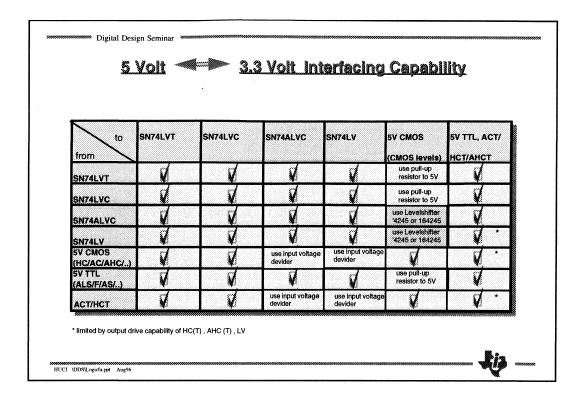

Before discussing the special requirements of mixed mode designs (i.e. systems, where there is a need to interface between the 5V and the 3.3V part), we would like to briefly discuss the different voltage level specifications used in both environments.

During the development of the 3.3V specification in JEDEC, there were basically two "interest groups" endorsing slightly different proposals.

The LV-CMOS proposal was mainly targeted to mobile applications, where battery operation requires a  $V_{\rm CC}$  min of 2.7V.

This proposal favoured a concept that basically copied the 5V CMOS one, i.e. an output voltage swing that almost equals  $V_{CC}$ , where  $V_{OL} \sim 0V$  and  $V_{OH} \sim V_{CC}$ . This would allow the proper operation of existing 5V CMOS devices from 3.3V ("Scaled CMOS").

On the other hand, the LV-TTL proposal favoured  $V_{\rm O}/V_{\rm I}$  specifications that are identical with 5V TTL, go that interfacing the two worlds is greatly eased.

Fortunately, the final 3.3V specification agreed upon by JEDEC covers both proposals.

It specifies a 2.7-3.6V  $V_{CC}$  range, in which the max/min values of the logic input levels are identical with the 5V TTL spec (0.8/2.0V) and max/min values of the logic output levels match the CMOS spec.

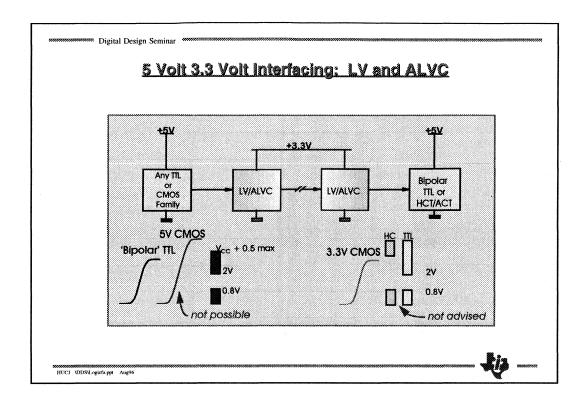

As has been explained on the previous page, both LV and ALVC do not allow input voltages higher than  $V_{\rm CC}$  + 0.5V.

However, this does not necessarily mean that these technologies are unable to interface with 5V signals.

If a 5V TTL signal is applied, its High level will typically be about 3.2V. This does not violate the LV or ALVC inputs specifications. One will have to make sure, however, that no overshoots can occur on the line which might again cause trouble.

On the output side, both LV and ALVC can directly drive 5V inputs that are TTL-compatible. No additional provisions will have to be made.

If the 5V receiver expects to see CMOS levels a special 'Level-Shifter' is required.

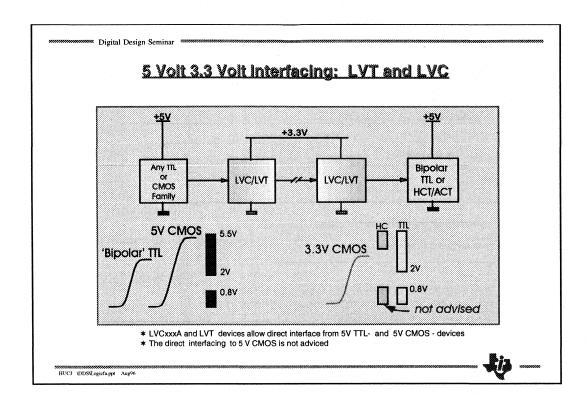

Both LVC and LVT allow input voltages to go up to 6.5V.

It means that these technologies can interface directly to 5V signals. Care needs to be taken, however, when driving the inputs from a 5V CMOS device, as possible overshoots may lead to the maximum LVC/LVT input voltage being exceeded.

On the output side, LVC and LVT can again (like LV and ALVC) directly drive 5V inputs that are TTL-compatible. No additional provisions will have to be made.

If the 5V receiver expects to see CMOS levels a special 'Level-Shifter' is required.

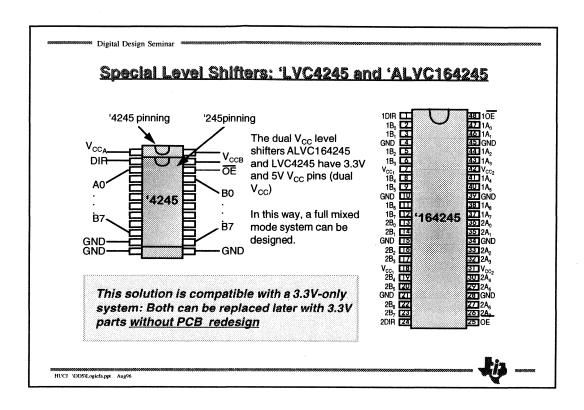

Certain applications will require a 'Level-Shifter' between 3.3V and 5V that can provide 5V output signals. Examples are:

- 1) interfaces to 5V CMOS-level devices which, as shown on the previous page, cannot be operated reliably from 3.3V outputs, or

- 2) 5V memory modules that should be connected to 3.3V components.

In the latter case a designer might want to provide a true 5V input signal to the memory, even if it has a TTL-type input, as the memory circuit's current consumption will otherwise be increased.

In these cases a dual  $V_{CC}$  level shifter will be required. This is a device that is connected both to the 5V and the 3.3V supply voltages such that it can independently access to and interface between both sides.

Here are two level shifter examples. The LVC4245 is an 8-bit version and the ALVC164245 is a 16-bit version, both with true 5V ↔ 3.3V level translation. Both devices are, or will be, offered by Texas Instruments.

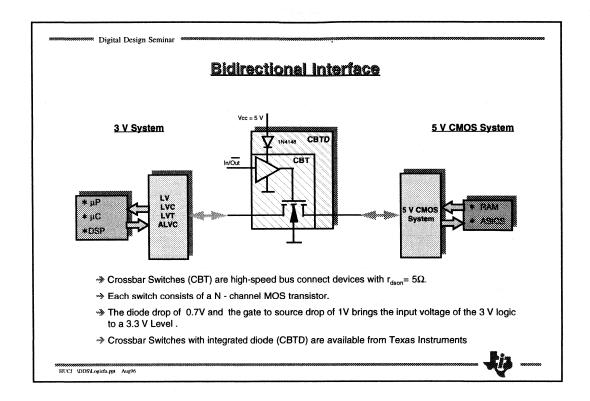

If a device with the capability to switch bus signals on or off is needed, then TI's CBT devices can be used to support easy bus communication.

CBT devices serve a number of unique applications in PC, Workstation, Bus Board, Telecom, Industry and Hard Drive end-equipment markets.

A CBT switch consists of simple n-channel MOS transistors. When the switch is open, it provides isolation (3-state) for the bus line. When the switch is closed, it imposes a near-zero propagation delay on the line (250 ps).

In multiprocessor systems, CBT can be used for extremely fast bus connections, bus exchanges in crossbar systems, memory interleaving, bus byte-swapping and a variety of other switching functions. CBT switches also serve as 5-V to 3.3-V bus translators, helping designers to mix devices of different voltage levels in the same system.

Crossbar Scwitches with integrated diode (CBTD) are available from Texas Instruments.

Extremely low propagation delays of 250 ps make CBT devices an effective replacement for drivers and receivers in high-speed systems, where signal buffering is not required.

In addition, low power consumption helps to improve battery life in portable systems. Small foot-print packages save board space.

Four different signal level constellations may have to be addressed in mixed mode design:

$\begin{array}{cccc} 5V \ TTL & \rightarrow & 3.3V \ TTL \\ 3.3V \ TTL & \rightarrow & 5V \ TTL \\ 5V \ CMOS & \rightarrow & 3.3V \ TTL \\ 3.3V \ TTL & \rightarrow & 5V \ CMOS \end{array}$

While the first two are very easy to address, the last two are difficult, as a certain technology may not support their requirements. LVC and LVT have I/Os that are 5V CMOS-tolerant. Interfacing a 3.3V part to a 5V system that expects CMOS levels, however, usually requires a dedicated level shifter. CMOS levels are specified as follows:

$$V_{IL} = 0.3 \times V_{CC}$$

$V_{IH} = 0.7 \times V_{CC}$

The driver should at least be able to deliver:

$$V_{OL}$$

< 0.3 x  $V_{CCmin}$ = 1.35V (with  $V_{CCmin}$  = 4.5V)

$V_{OH}$ > 0.7 x  $V_{CCmax}$ = 3.85V (with  $V_{CCmax}$  = 5.5V)

This also implies that a standard 3.3V output does not deliver a high enough output voltage to reliably drive 5V CMOS inputs.

Even with a pull-up resistor

$$V_{Omax} = V_{CCmin} + 0.7V \text{ (diode)} = 3.7V < 3.85V$$

the result is the following: a special 'Level-Shifter' is required.

TI has addressed many important design issues including testability, memory driving, bus termination, low skew requirements, and low-impedance line driving with specialized, advanced logic devices that improve overall system performance.

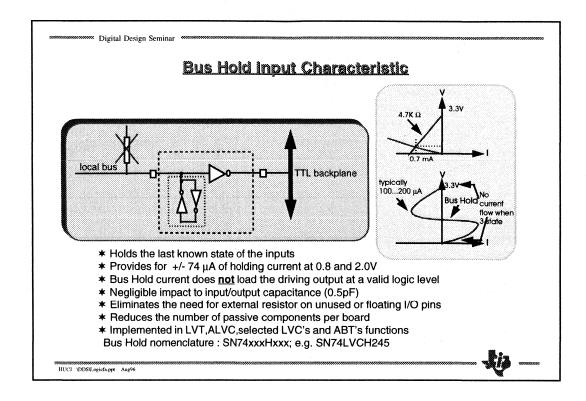

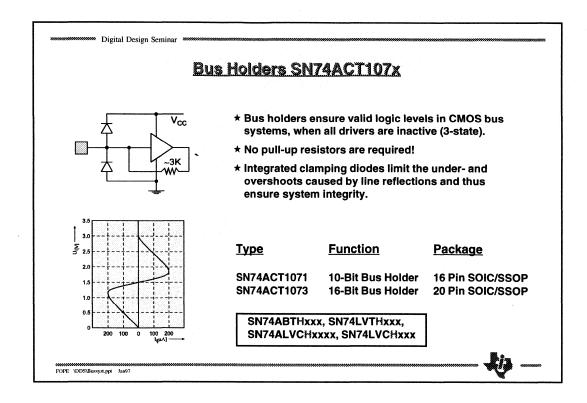

This figure shows the typical V-I characteristics of a bus line with pull-up resistors versus a bus line using a bus interface device with integrated bus hold. The bus hold circuit basically consists of a non-inverting driver that will drive a small current (typically peak value is about 100-200  $\mu$ A) back into the bus, to pull it back to proper signal levels, if the bus is floating.

As can be seen, the pull-up solution causes a constant current to flow on both ends. The bus hold circuit, on the other hand, not only consumes much less current, but also does not represent any static loading to the bus. This means that it will not consume any current, as long as the bus is at a proper Low or High level.

The Bus Hold feature has been implemented in the LVT and ALVC family as well as in selected LVC and ABT functions.

Look for the 'H' within a device nomenclature.

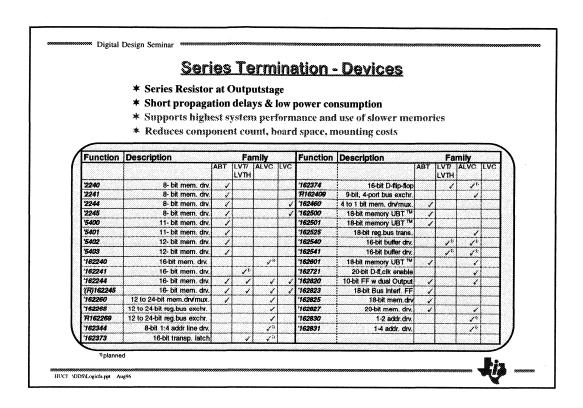

One line termination technique, which was already mentioned earlier is the so-called Series Termination.

As opposed to most other termination techniques (where the lines are terminated at the end), here the driver output impedance is matched with the line impedance by adding a series resistor. This means that no reflection will occur on the driver side.

It is thus a very efficient method for a point-to-point connection, or for a line driving a concentrated load. This technique is especially useful when driving memory array address lines as it suppresses signal under- and overshoots which may otherwise lead to data loss.

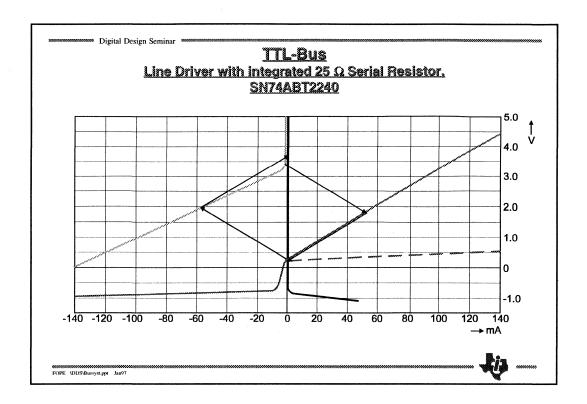

Several 5-V and 3.3-V logic devices are available with an integrated output resistor. The resistor value is typically around  $25\Omega$ , leading to an effective output resistance of about  $33\Omega$ .

As a certain impedance mismatch is acceptable, these circuits will be feasible for line impedances up to approximately  $75\Omega$ .

\*\* Digital Design Seminar Texas Instruments IEEE 1149.1 Products Boundary scan products allow easy test of high-density boards Benefits using IEEE1149.1 **★** SCOPE<sup>TM</sup> bus drivers support most applications \* Test node access on high-density demanding boundary scan functions board \* Path support functions allow easy handling Inexpensive test adapters of scan path's in large systems \* Std interface for ICs, boards, systems \* Easy to implement in ASICs ★ Broad spectrum of bus driver functions ★ 3.3-volt drivers already on the market ★ Support from IC and ÁTE vendors **Product features** \* State-of-the-art techniques used ★ Popular bus driver functions available ★ 3.3-volt versions IEEE1149.1 was developed by the Joint Test Action Group (JTAG) ★ Universal-Bus-Transceivers available SCOPE (System Controllability Oberservability Partitioning Environment) is a trademark of Texas Instruments Incorporated ★ Functions available for large systems HUCJ \DDS\Logicfa.ppt Aug96

Scope<sup>TM</sup> products from Texas Instruments comply with the IEEE1149.1 specification. Scope products are offered in BICMOS technology (ABT and LVT) and Advanced CMOS (ACT).

The nomenclature includes an '8' to express its testability feature (e.g SN74ABT8245, which is a '245 function additionally supporting testability (IEEE1149.1).

The widebus devices including this feature can be recognized with '18' instead of '16' (e.g SN74.LVT18502).

## The generic IEEE1149.1 function:

Between each IC pin (input and output) and the chip functional logic there is a boundary scan cell (BSC).

All BSCs are connected to a serial scan path with the function of a shift register.

The BSCs are to be controlled via 4 control pins: TCK (test clock), TMS (test mode select), TDI (test data input), TDO (test data output).

The BSC allows capturing data from and providing data to the chip data path.

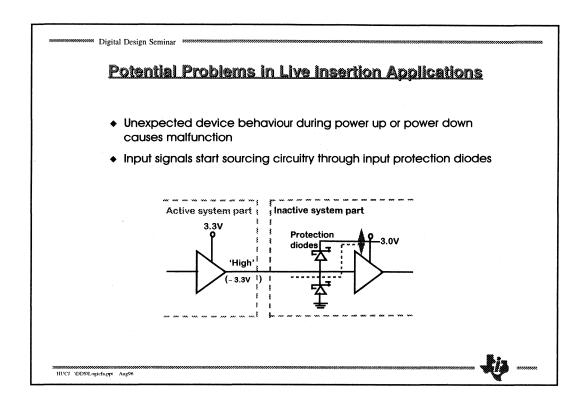

Along with the power reduction trend that drove the transition to 3.3V, live insertion has become of much more interest in system design. Also, so-called "partial power down" is being applied more frequently, where the supply voltage  $V_{CC}$  will be switched off in certain parts of the system, while these are not in use.

In both cases (live insertion and partial power down), there are two potential problems that need to be addressed. First, there is a risk of unexpected device behaviour during the power transition. All logic circuits available in the market have specifications that guarantee proper circuit operation only within a certain  $V_{\rm CC}$  range. During power up or power down, the circuit will be operated outside this range, which may lead to an unpredictable device response. For example, the output may start sinking large currents or, worst case, even start oscillating.

Second, the block diagram shows a constellation, where an active device output is connected to a device, whose  $V_{CC}$  has been switched off. In this special case, the inactive circuit uses protection diodes as its inputs. This method is being used in many CMOS circuits for ESD protection. Unfortunately, a high signal applied to this input will be fed to the circuit's  $V_{CC}$  connection via the protection diode. The  $V_{CC}$  level of the inactive circuit will be about 3.0V, which is high enough to activate this circuit and (via the  $V_{CC}$  path) the remaining devices in the inactive system part. This may result in all kinds of unexpected system behaviour.

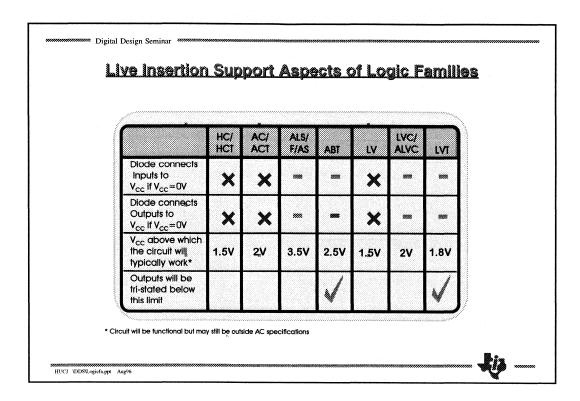

This table illustrates the feasibility of using certain logic families for live insertion applications.

As can be seen, the 5V families HC/HCT and AC/ACT, as well as the 3.3V family LV, will be difficult to use in any live insertion applications. This is mainly, because they all use protection diodes that connect the inputs and outputs to  $V_{\rm CC}$ .

Those families that do not use protection diodes to  $V_{CC}$  will be easier to design with. However, only 5V ABT and 3.3V LVT circuits feature full live insertion support, as they also comprise a "power-up 3-state" circuitry that will 3-state the device outputs, if  $V_{CC}$  is below a certain limit. A system designer can thus easily design interfaces that allow reliable power-down operation.

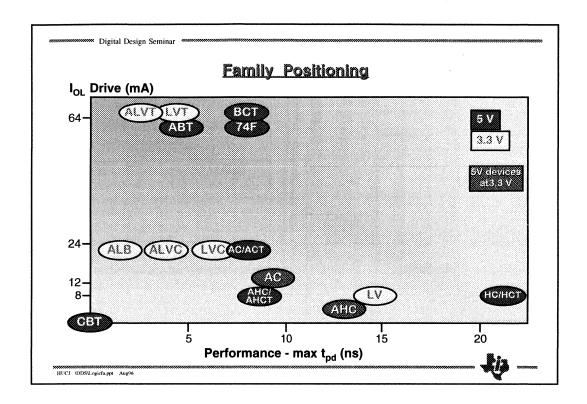

Plotting  $I_{OL}$  vs  $t_{pd}$  we see that the 3.3V families (ALB, LV, LVC, ALVC, LVT and ALVT) and the 5V logic families (ABT, AC/T, AHC/T and CBT) cover the whole range of required performance nodes.

For reference, some 5-V families (AHC and AC) are also shown with their performance parameters, when operated with 3.3V.

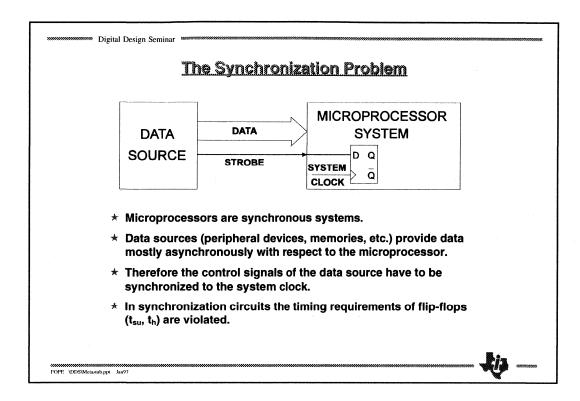

Standard microprocessor systems are synchronous systems, which means that there is a common clock signal that feeds the clock inputs of all flip-flops in the system. Under these circumstances it's easy to fulfill the set-up and hold-time requirements of all flip-flops.

It's a common situation that external data has to be transferred into a microprocessor system and mostly the external equipment is running asynchronously to the clock of the microprocessor system. In this situation it's usual to put the new data-word onto the data-lines and use a separate strobe line to indicate the presence of the new data. Anywhere within the microprocessor this strobe signal will be stored in a flip-flop, whose clock is synchronous to the microprocessor clock.

Under these circumstances the designer can not ensure that the set-up or hold-time requirements of this flip-flop will be fulfilled. If a violation of the set-up or hold-time takes place, the manufacturer of the flip-flop will no longer guarantee proper function and the system may malfunction.

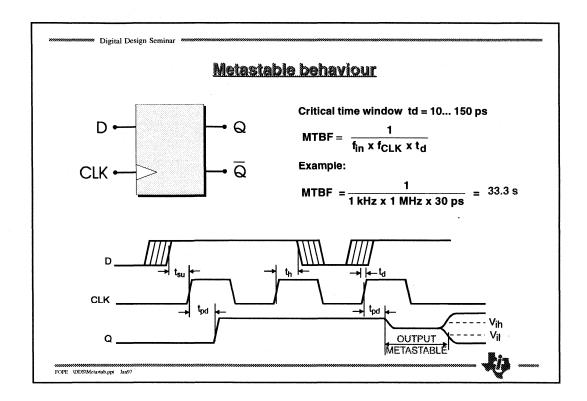

Every flip-flop data-sheet specifies a set-up and a hold time. The set-up and hold-time define a time window around the active (mostly rising) edge of the clock signal, where it is not allowed to change the signal at the D-input. If the signal at the D-input changes within the forbidden set-up and hold-time window, one of two reactions of the flip-flop can be observed:

- 1) The flip-flop works perfectly with no special behaviour

- 2) The output of the flip-flop becomes metastable

If the output of a flip-flop is metastable, the voltage value  $V_{\rm O}$  is higher than the  $V_{\rm il}$  low-level-limit, but lower than the high-level-limit  $V_{\rm ih}$ : It is in the forbidden area between low and high. This situation can last less than 1ns, but could also last longer than 30ns. This normally is a major problem for the input of the circuit that gets its signal from this metastable flip-flop.

Because it's not possible to avoid this situation by design, the only way to deal with it is statistically. The value used here is MTBF (Meantime between failure) and can be calculated using the following formula:

$$MTBF = \frac{1}{f_{in} \times f_{CLK} \times t_d}$$

with f<sub>in</sub>: Data rate at D-input

f<sub>CLK</sub>: Clock frequency

t<sub>d</sub>: Critical time window

The set-up and hold-time window is a time window guaranteed by the manufacturer of the flip-flop, guaranteed over the temperature range, supply voltage range and production variations. If the signal at the D-input changes within the critical time windows  $t_{\rm d}$ , then the flip-flop will become metastable. The above example with MTBF = 33.3s shows a unacceptable situation.

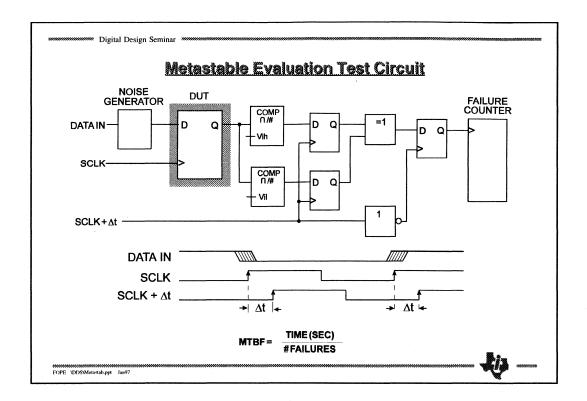

To find out the metastable behaviour of the flip-flops from Texas Instruments, the applications lab has made measurements with the above setup:

The flip-flop under test (DUT) gets a stable clock signal and a data signal with some jitter. The output of the flip-flop is connected to two comparators, one for the comparison against a valid logic high level  $V_{ih}$  and one for the valid logic low level  $V_{il}$ . The result of this comparison is stored in two flip-flops, whose clock signal is the delayed clock of the tested flip-flop (DUT). The following EXOR gate filters the errors and sends them to a ordinary counter.

With the amount of delay that is added to the clock signal of the two comparators flip-flops, we give some time to the tested flip-flop to make the decision between a logic high- and low-level. If the flip-flop wasn't able to make this decision within the specified time-frame, and the output of the flip-flop is still within the forbidden voltage area, a metastable state will be counted with the failure counter.

Some of these tests have to be running over several days to find a reasonable number of metastable conditions.

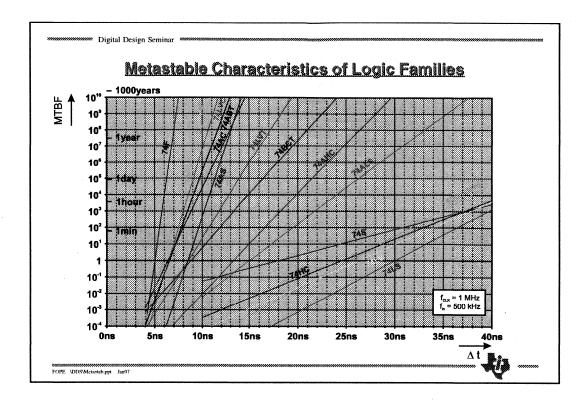

The Applications Lab of Texas Instruments measured the flip-flop of all available product families with the test set-up described one page before. The result of these measurements can be seen in the above diagram.

In X-direction the diagram shows  $\Delta t$ , the time-frame the flip-flop gets to make a decision for high or low, and the Y-axis applies to the resulting meantime between failure (MTBF) rate.

These curves have been measured with a clock frequency of 1MHz and an input data rate of 500 kHz.

Digital Design Seminar

## Mean Time between Failures of a Synchronizer

$$\text{MTBF} = \ \frac{e^{(T \, \times \, \Delta t)}}{f_{in} \, \times \, f_{CLK} \, \times \, T_0}$$

- ★ There is no way to avoid metastable states in synchronization circuits.

- **★** Fast Logic Circuits return quicker from a metastable to a stable state.

- ★ The probability of system failures is greatly reduced by a delayed test of the synchronization circuit.

|        | T [ns-1] | T <sub>o</sub> [s] |  |

|--------|----------|--------------------|--|

| 74STD  | 0,74     | 2,9E-4             |  |

| 74LS   | 0.72     | 4.8E-3             |  |

| 748    | 0.36     | 1.3E-9             |  |

| 74ALS  | 1.02     | 8.8E-6             |  |

| 74AS   | 4.03     | 1.4E3              |  |

| 74F    | 9.20     | 1.9E8              |  |

| 74BCT  | 1.51     | 1.14E-6            |  |

| 47ABT  | 3.61     | 0.033              |  |

| 74HC   | 0.55     | 1.48E-6            |  |

| 74AHC  | 1.41     | 2.9E-4             |  |

| 74AC   | 2.80     | 1.1E-4             |  |

| 74LV   | 0.60     | 1.38E-5            |  |

| 74LVC  | 4.40     | 4.008              |  |

| 74ALVC | 4.60     | 1.047              |  |

| 74LVT  | 2.13     | 1.52E-4            |  |

FOPE \DDS\Metastab.ppt Jan97

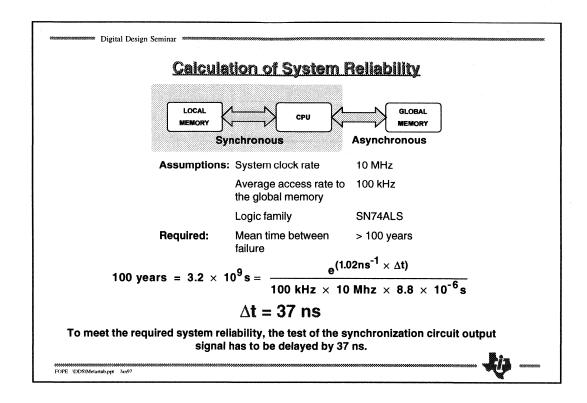

The following equation is the mathematical representation of the graphs on the previous page:

$\text{MTBF} = \ \frac{e^{\left(T \, \times \, \Delta t\right)}}{f_{\text{in}} \, \times \, f_{\text{CLK}} \, \times \, T_{0}}$

with f<sub>in</sub>:

Data rate at D-input

f<sub>CLK</sub>:

Clock frequency

T and T<sub>0</sub>:

Constants describing the device family characteristics

Δt:

time for the flip-flop to decide between high or low

With this equation it's possible to calculate the MTBF rate of a specific circuit design.

In the above example a CPU, running with 10MHz clock frequency, accesses a external global memory with an average data-rate of 100kHz. The designer wants to use a SN74ALS flip-flop and needs a meantime between failure rate of 100 years. Using the equation of the page before,  $\Delta t$  can be calculated to be 37 ns. This means, that if the CPU waits 37ns after the active clock edge before it looks at the output of the SN74ALS flip-flop, an MTBF rate of 100 years is achieved.

In the first example (page 3-2) the metastable states could be supervised by intelligent software: The CPU looks at the STROBE signal twice before it accepts the logic state.

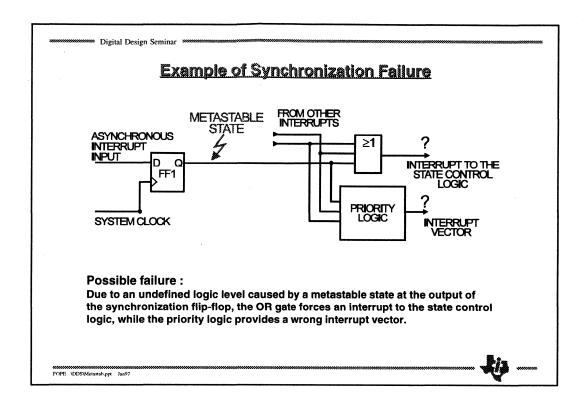

The example above shows a situation where metastability must be solved by hardware. Assume the output of the interrupt flip-flop is metastable and correspondingly the logic level is undefined. The gate that sends the interrupt to the CPU can detect a valid interrupt while the priority logic takes the same signal and decides that there is actually no interrupt. Therefore an interrupt occurs, but no interrupt (or a wrong) vector is sent to the CPU. In this case the CPU will jump to a no existing interrupt service routine and a system crash will be the result.

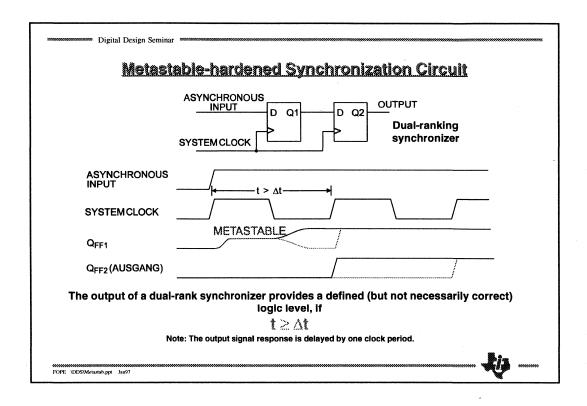

To increase the MTBF rate a further circuit design method is available: The Dual-Rank Synchronizer. Here we take two flip-flops and connect them as a shift-register. In this case the output of the second flip-flop will be less often in a metastable condition than the output of the first flip-flop. Three situations can occur when flip-flop 1 is in metastable state:

- The metastable state of the first flip-flop is short enough, so at the next rising edge of the clock signal the second flip-flop already gets a good signal at its D-input.

- 2) The metastable state of the first flip-flop lasts longer than one clock period, but the second flip-flop accepts the undefined signal as a valid high or low state.

- 3) The metastable state of the first flip-flop lasts longer than one clock period and the second flip-flop becomes metastable, too.

In the first two cases the output of the second flip-flop is not metastable, while the first one is metastable. This shows the reduction of metastable states with this circuit.

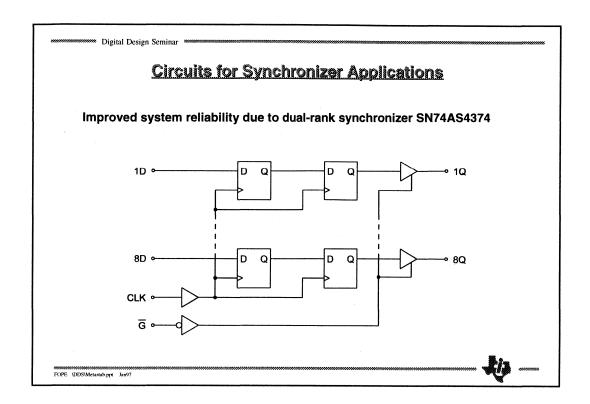

Because dual-rank synchronizers are a common way to reduce the occurrence of metastable states, Texas Instruments invented the SN74AS4374. This circuit has nearly the same function as the well known octal flip-flop SN74AS374, with the only difference that there is a dual-rank synchronizer instead of a single flip-flop in each data-path. Here no extra board space and no redesign is necessary to upgrade a single flip-flop synchronizer to a dual-rank synchronizer.

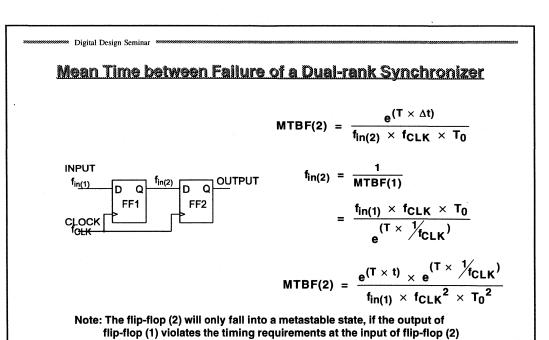

To calculate the MTBF rate of a dual rank synchronizer only the metastability of the second flip-flop is of interest. Here we use the previously discussed formula:

$$MTBF = \frac{e^{(T \times \Delta t)}}{f_{in} \times f_{CLK} \times T_0}$$

It's not possible to generate a metastable state at the output of the second flip-flop if the first flip-flop is working well. To drive the second flip-flop into metastable condition a metastable state of the first flip-flop is necessary. Hence the input data of flip-flop two that is of interest regarding metastability is only the situation where the first flip-flop is metastable. So the reciprocal MTBF value of the first flip-flop can be used as input data rate of the second flip-flop.

$$f_{in(2)} = \frac{1}{MTBF(1)} = \frac{f_{in(1)} \times f_{CLK} \times T_0}{e^{(T \times \sqrt{f_{CLK}})}}$$

Now the final formula can be calculated:

FOPE \DDS\Metastab.ppt Jan97

$$MTBF(2) = \frac{e^{(T \times t)} \times e^{(T \times \frac{1}{f_{CLK}})}}{f_{in(1)} \times f_{CLK}^2 \times T_0^2}$$

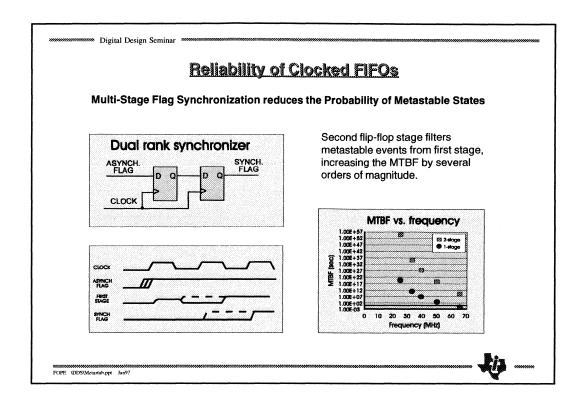

Texas Instruments offers FIFO (first-in-first-out) memories. One key feature here is the possibility of asynchronous write and read operations. This is a product where metastability is a major issue and Texas Instruments uses at least dual-rank synchronizers to avoid metastable conditions at the outputs.

During the design phase investigations took place to find out the MTBF rate of FIFOs with and without dual-rank synchronizers. The result of these investigations can be seen in above diagram. For example at a clock frequency of 50 MHz the single flip-flop synchronizer shows a MTBF rate in the range of several minutes, while the dual-rank synchronizer is in the range of  $10^{19}$  seconds or  $3.17 \times 10^{11}$  years.

This example shows the tremendous improvement this type of circuit design can achieve regarding metastable behaviour.

Noise in digital logic systems arises from different sources:

- External noise radiated into the system

- Power-line noise coupled through the AC and DC power distribution system

- Cross talk induced into signal lines from adjacent signal lines

- Signal- and supply-current spikes caused by switching several loads

- Transmission-line reflection from unterminated transmission lines.

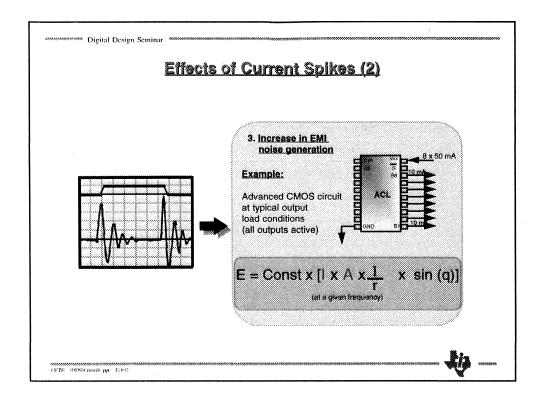

A major noise source is the integrated circuit, simply because of its high-speed switching.

As can be seen from the formula, a circuit's slew rate corresponds to the transition (rise or fall) time of the output signal. The shorter the rise or fall time, the higher the slew rate.

Knowing about the slew rate is a good way to get a rough estimation on the noise potential of the device in use. However, keep in mind that propagation delay and slew rate are not necessarily proportional.

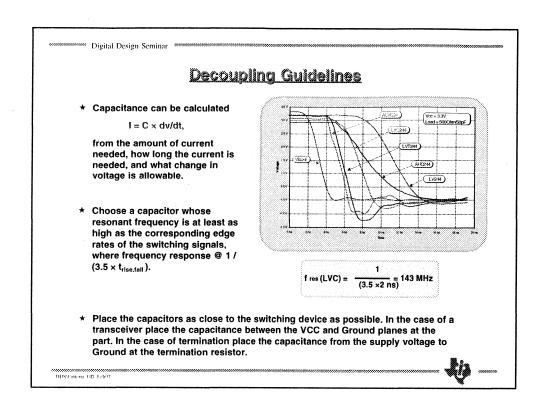

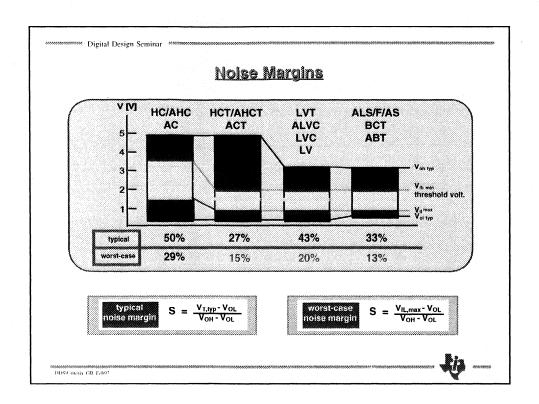

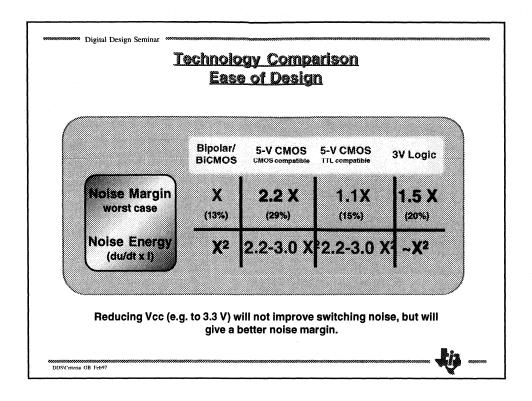

This table shows the propagation delay,  $t_{pd}$ , voltage swing,  $(V_{OH} - V_{OL})$ , slew rate, and dv/dt for selected logic families. HC, AHC, ALS, AC, F and ABT operate from a 5V supply voltage, while AHC, LV, LVC, LVT and ALVC have a 3.3V supply. The data indicates that  $t_{pd}$  and dv/dt show common trends (the shorter the propagation delay, the higher the slew rate). However, there is no direct link between the two parameters. In particular, the fastest family is not the one with the highest slew rate.

This must be considered especially when designing high speed systems. As will be discussed later in this section, high slew rates are very unfavorable as they design in high noise levels generated by the components. The worst technology in this respect is 5V AC. All of the low voltage technologies have somewhat lower signal slew rates.

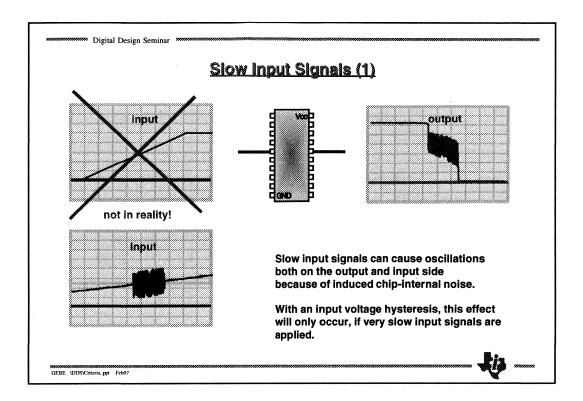

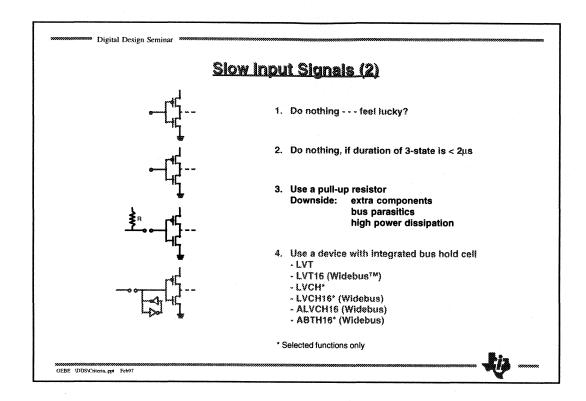

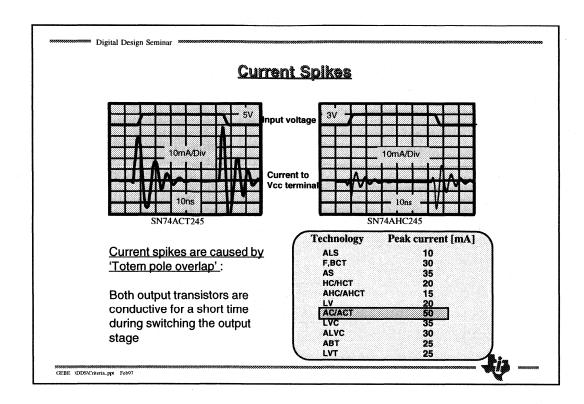

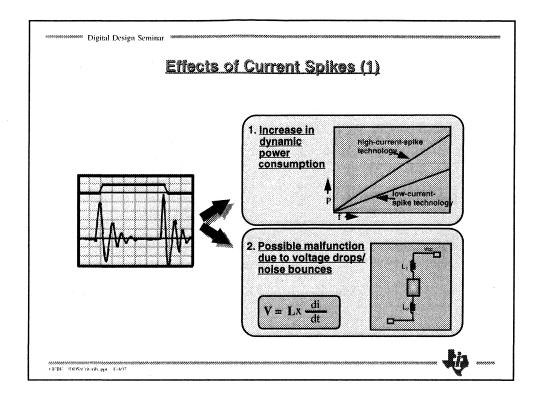

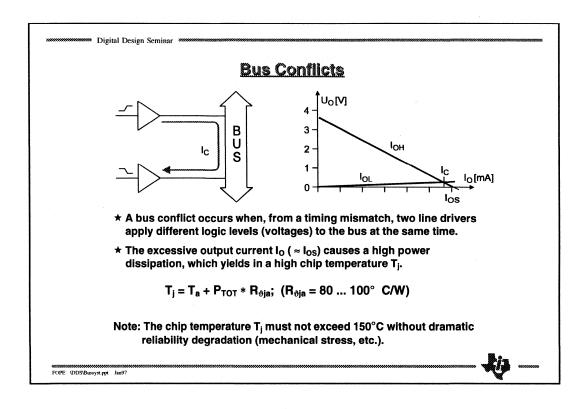

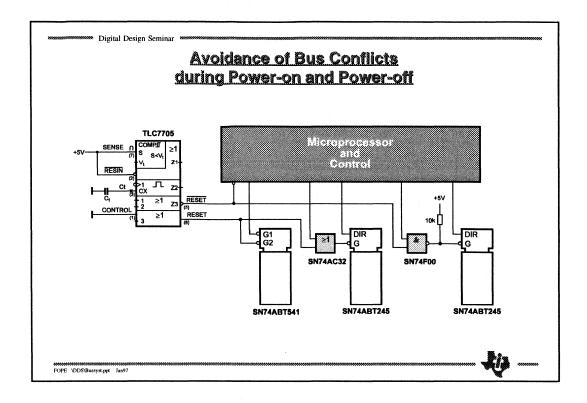

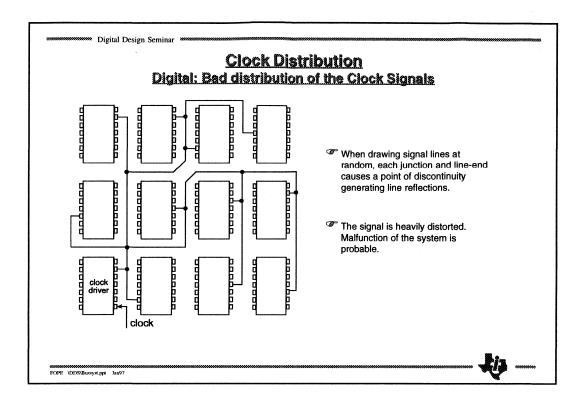

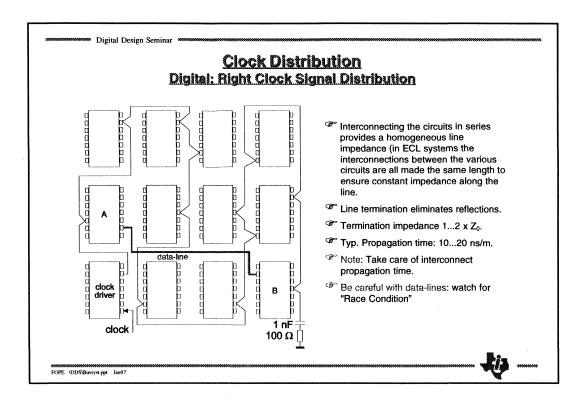

It should be especially noted that ALVC, the fastest of all technologies shown, exhibits a comparably low slew rate. This is due to appropriate circuit design techniques and the SSOP/TSSOP package technology used for these 16- to 20-bit bus interface functions.